Hi,experts

I've been studying how to use GPIO interrupt recently.

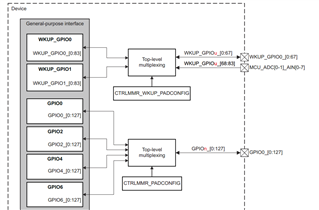

I want to change the pin AC4 of GPIO0 to general GPIO and use its interrupt on MCU2_0.

But I see the following link saying:

GPIO0 is allocated to A72

Is that true? Does this mean that MCU2_0 or other cores cannot access gpio0?

However, the pins of SPI0 and SPI1 also belong to GPIO0 .

Can only A72 access SPI0 and SPI1?

Best Regards,

Tao