I have read the forum FAQ, the link is below:

I have questions:

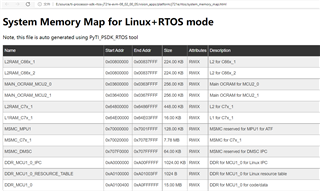

1. why "The SOC address space 0x800000000 - 0x87FFFFFFF is permanently disabled on TDA4VM. There is no software configuration to change this."

2. If the first 2GB memory region in external SDRAM high memory region is inaccessible, why the region of high memory region is 0x80 0000 0000 - 0xFF FFFF FFFF, why not 0x89 0000 0000 - 0xFF FFFF FFFF?