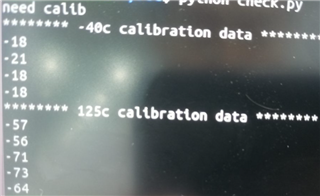

on the errorate i2128 It is described that the sensor sensor is calibrated at the factory, and the calibrated 5 temperature sensor data are written in VTM EFUSEx.

in the errorate i2128,VTM efuse story 5 temperature sensor calibrated data,but on the sdk7.3;iThe calibration data of the first temperature sensor is used as the calibration data of 5 temperature sensors。

my question is:

1,Why not use the calibration data for each temperature sensor individually to correct?

2,Is it because the bias of each sensor is consistent? Is this conclusion based on batch data from production? how mach is the calibration deviation of the 5 sensors?

on the sdk7.3 patch csl_pvt_sensor_lut.h There are two lookup tables here:

gCSL_pvt_poly_golden:Same as the function in the TDA4 TRM manual

gCSL_pvt_poly: I don't know where this table came from

my question is:

1,Why are there two tables and what do they mean?

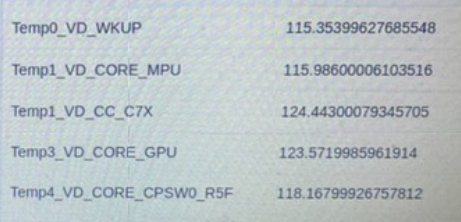

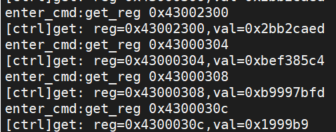

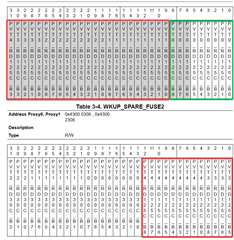

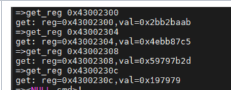

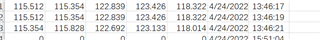

the VTM_EFUSE data is that

the VTM_EFUSE data is that in the sprz455b.pdf i2128: In the picture, the green box is the value used in the program to cover 5 sensors.

in the sprz455b.pdf i2128: In the picture, the green box is the value used in the program to cover 5 sensors. , each value is different,How to understand the 5 values in this and how they are different?

, each value is different,How to understand the 5 values in this and how they are different?

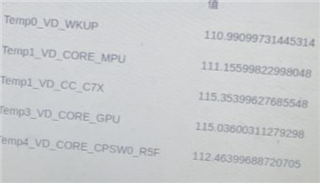

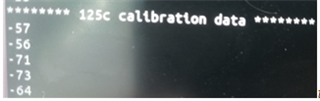

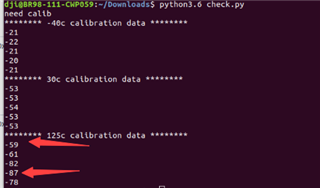

28 point;Looking up the table, it can be seen that there will be 4 ℃

28 point;Looking up the table, it can be seen that there will be 4 ℃ sensor 3&4 is 8 higher than sensor 1

sensor 3&4 is 8 higher than sensor 1