Hi expert,

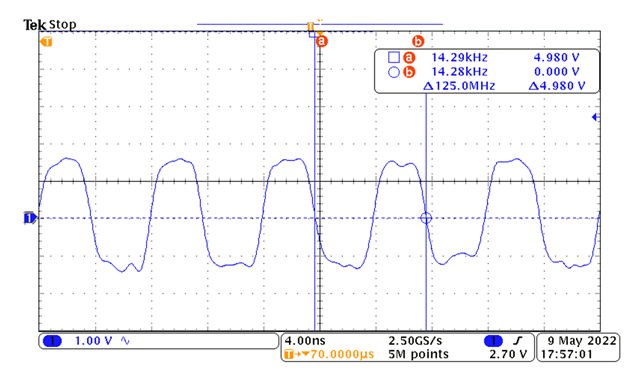

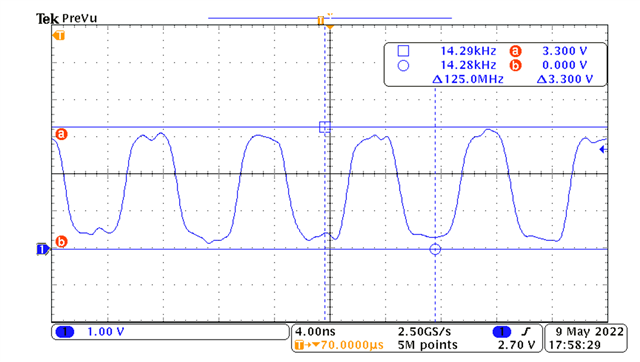

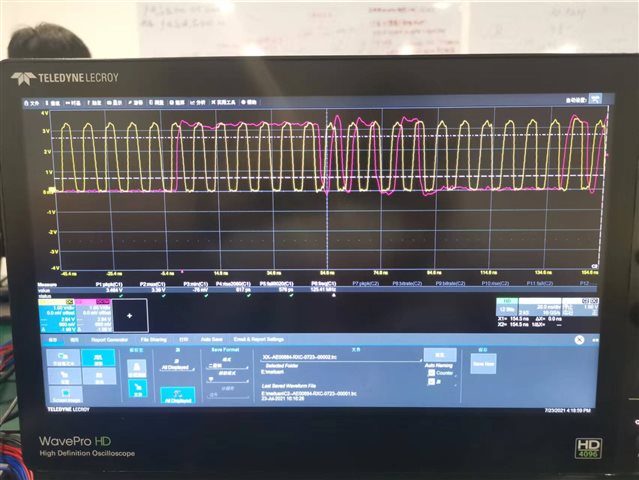

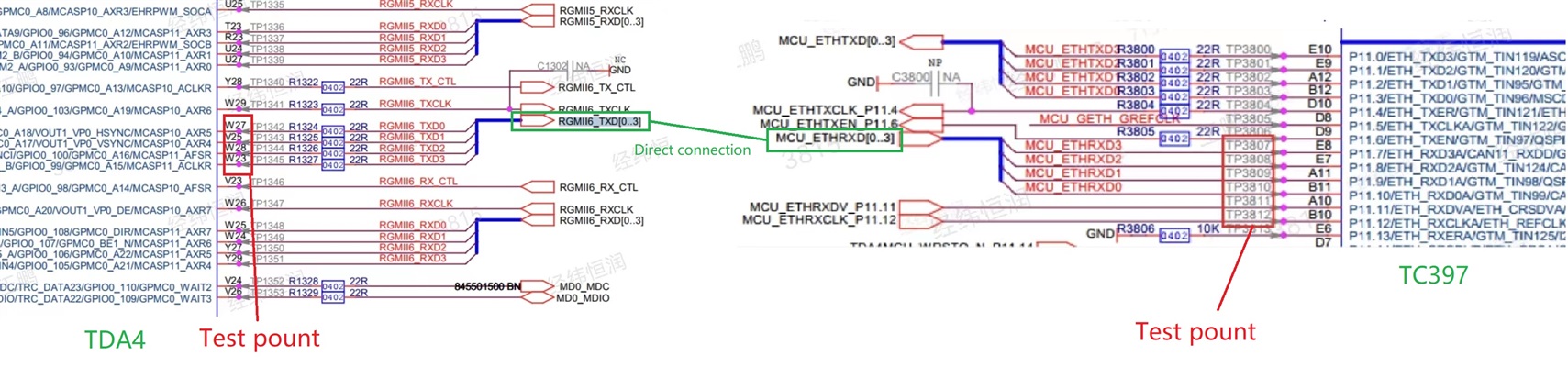

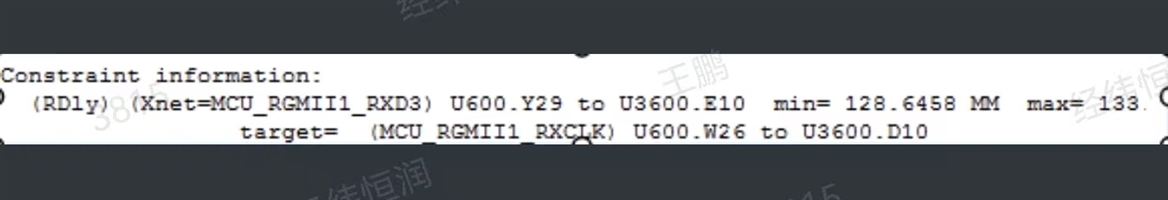

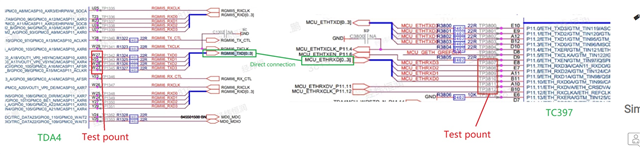

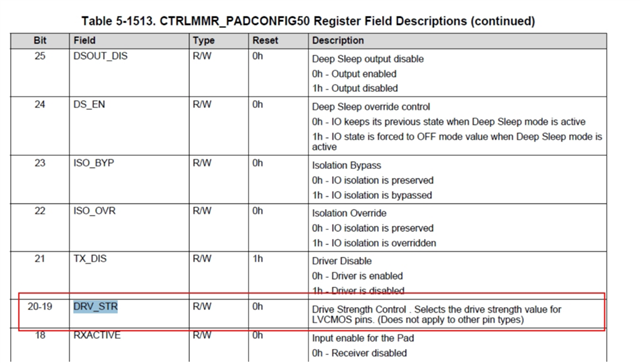

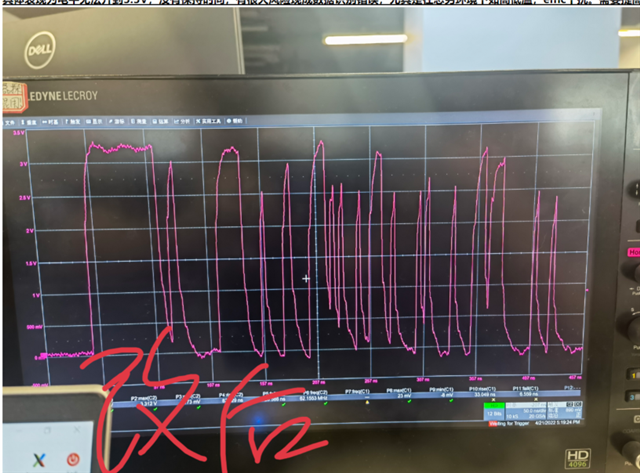

At present, the hardware test indicate that the rgmii TXD data of tda4 shows insufficient driving ability, the level cannot rise to 3.3V, there is no holding time, and the driving ability of the pin is still not improved after modification (the modified register is as follows)

The specific performance is that the level cannot rise to 3.3V, there is no holding time, and there is a great risk of ready-made data identification errors, especially in harsh environments such as high and low temperature and EMC interference. As It is necessary to improve the signal output power of tda4

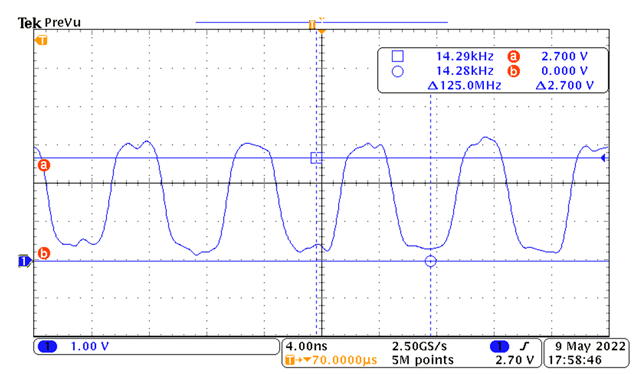

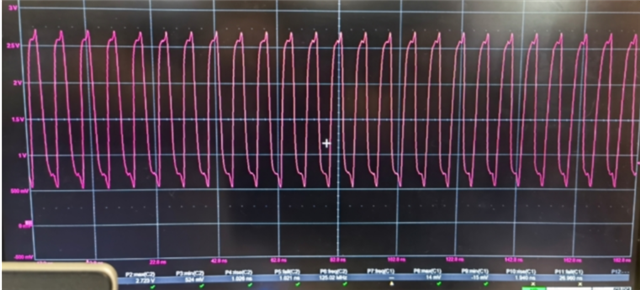

In addition, the output rgmiitx clock signal of tda4 is not good, and there is also the problem of insufficient output capacity, between 0.5-2.7v (normal 0-3.3v)

So is there any way to solve the problem of insufficient rgmii driving ability and whether other information input is needed.

These problems seriously affect the hard test and product stability. Please pay attention and support to solve them. Thank you