Other Parts Discussed in Thread: DRA821,

Hi Champs

There's an issue that a customer wants to solve about CPSW-5g and SGMII.

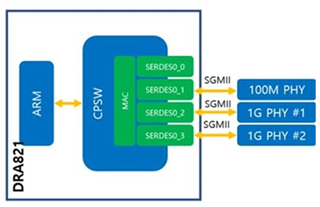

Three PHYs were connected through SGMII as below.

Test Conditions :

1. All the SGMIIs are connected to the Capacitor 100nF.

2. All PHY inputs and outputs consists of CML circuit.

3. SDK version : PSDK v8.1

4. Traffic load uses Spirit C1 equitment.

Issues 1. (100Base-T1 related)

Scenario #1

- Path : A72 - CPSW - PHY - PC

- Problem : During the two-way test of ping between ARM and PC, the path of 100M PHY is packet loss. However No packet loss when using other 1G PHYs.

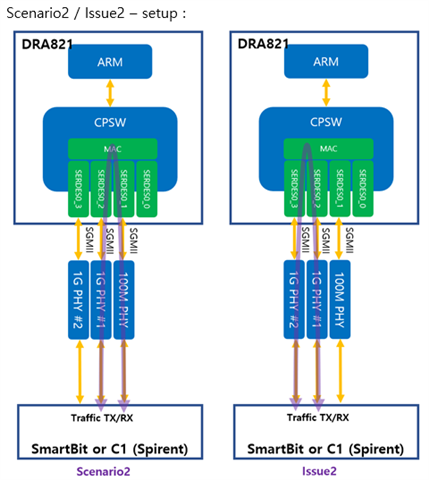

Scenario #2

- Path : 1G PHY #1 - CPSW - 100M PHY

- Problem : Packet loss occurs when transmitting and receiving 100Mbps of traffic.

- Remark : Only occurs in the 1G PHY -> 100M PHY direction

Attachments :

- after AP_CAP : DRA821 output waveform

- after PHY_CAP : DRA821 input waveform

Issues 2. (1000Base-T1 related)

- Path : 1G PHY #1 - CPSW - 1G PHY #2

- Problem : When Full traffic load of 1Gbps, Packet loss occurs only at CPSW output terminal even though CPSW input terminal does not have packet loss.

Common Info : Line loopback test of all PHYs confirmed no problem.

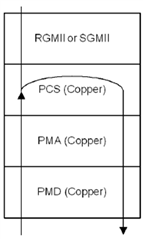

They believed the above issues appear to be related to the SGMII interface and CPSW

According to them, the strange thing is that if you test the speed at 999Mbps instead of 1Gbps, there will be no issue.

Please help and review as soon as possible.

Regards,

Jack