Dear expert,

According to this link https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1008072/tda4vm-ocm-data-retention-after-reset/3726546?tisearch=e2e-sitesearch&keymatch=PSRAM#3726546

MCU_PSRAM0_RAM 0x0040280000 0x00402801FF 512 B will reserved the value after warm reset. But I test this on TDA4VM and find it can't reserved the PSRAM0 of previous segment.

Test environment: SDK7.3 + SPL boot + SD card boot media

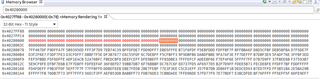

1. Use CCS to view memory before warm reset show as below

2.Through CCS set the memory of start address 0x0040280000 to zero

3. run warm reset code on MCU1_0 succeed show as below

volatile uint32_t enableDebug = 1;

do

{

}while (enableDebug);

int32_t status =CSL_PASS;

status = Sciclient_pmDeviceReset(SCICLIENT_SERVICE_WAIT_FOREVER);

if(status==CSL_PASS)

{

printf("Reset completed, but this is not reset!!!\n");

}

else{

printf("Reset failed!!!\n");

}

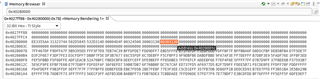

4.After warm reset the memory of value show as below

It looks like this memory was changed after a warm reset. Is there some program using this memory space? Is have other memory space can reserved value after warm reset?