Hi, TI

We have a new OSPI Flash device MT35XL01GABA1G12 in our custom board and want boot from this OSPI Flash device.

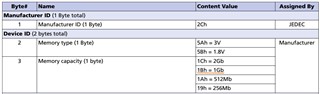

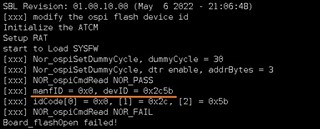

We just change the BOARD_FLASH_ID_MT35XU512ABA1G12 from 0x5B1AU to 0x5B1BU in order to match our ospi flash device ID, but the SBL boot fail .

Is there any guide line for porting this device in RTOS SDK?

Our SDK version is 07.03.

BR.

Sancho