Hi Team,

There are 5 MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_x in TRM p4689-p4690, what is the exact definition on these signal, we are supporting customer to finish a diagnose system design, need this info

Thanks

Thomas

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

There are 5 MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_x in TRM p4689-p4690, what is the exact definition on these signal, we are supporting customer to finish a diagnose system design, need this info

Thanks

Thomas

Hello Thomas Yang55,

Thank you for the query.

I will have to check this internally.

In the mean time please share any additional detail that you may have on the customer use case that could help the team.

Regards,

Sreenivasa

Hello Thomas Yang55,

Sorry for the delay and thank you for following.

I am internally following and will prioritize on getting you an answer.

In the mean time please share any additional detail that you may have on the customer use case that could help the team.

Regard,

Sreenivasa

Hi Sreenivasa

The diagnose path is as below, as customer need to route POK signal to A53 core, not M4 core, so the path is a little complexity.

I am not very confident on the latency, do you have any suggestion or other comments?

Still waiting for your answer on above ticketed questions, thanks.

POK ---> ( as an event input - MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_0 - map to - MCU_ESM0_PLS_IN_78 of) > MCU_ESM > (then output as an interrupt - MCU_ESM0_ESM_INT_HI_LVL_0) ---> (as an event input - MCU_ESM0_ESM_INT_HI_LVL_0 - to - ESM0_LVL_IN_38) > ESM (then output as an interrupt - ESM0_ESM_INT_HI_LVL_0 ) ---> (interrupt) > GISS0 > ( as interrupt no - GICSS0_SPI_IN_181 to notify) ---> A53

Hello Thomas Yang55,

Thank you for following on this.

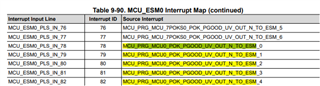

Please refer below table.

Regards,

Sreenivasa

| Interrupt Input Line | Interrupt ID | Source Interrupt in TRM | Updated Source Interrupt |

| MCU_ESM0_PLS_IN_78 | 78 | MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_0 | pok_vdd_mcu_uv |

| MCU_ESM0_PLS_IN_79 | 79 | MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_1 | pok_vdda_mcu_ov |

| MCU_ESM0_PLS_IN_80 | 80 | MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_2 | pok_vdda_mcu_uv |

| MCU_ESM0_PLS_IN_81 | 81 | MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_3 | pok_vdda_pmic_in_uv |

| MCU_ESM0_PLS_IN_82 | 82 | MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_4 | pok_vdd_mcu_ov |

Hello Thomas Yang55,

Thank you for the note. I have provided the answer for the previous query.

Regards,

Sreenivasa

Hello Thomas Yang55,

For the below query, i am checking internally. Do you have some additional inputs on the use case. I received the below comment

I do not quite understand the context of this query – why is this interrupt routing any different then any peripheral interrupt?

The diagnose path is as below, as customer need to route POK signal to A53 core, not M4 core, so the path is a little complexity.

I am not very confident on the latency, do you have any suggestion or other comments?

POK ---> ( as an event input - MCU_PRG_MCU0_POK_PGOOD_UV_OUT_N_TO_ESM_0 - map to - MCU_ESM0_PLS_IN_78 of) > MCU_ESM > (then output as an interrupt - MCU_ESM0_ESM_INT_HI_LVL_0) ---> (as an event input - MCU_ESM0_ESM_INT_HI_LVL_0 - to - ESM0_LVL_IN_38) > ESM (then output as an interrupt - ESM0_ESM_INT_HI_LVL_0 ) ---> (interrupt) > GISS0 > ( as interrupt no - GICSS0_SPI_IN_181 to notify) ---> A53

Regards,

Sreenivasa

Hello Thomas Yang55,

I have not heard from you and closing the thread.

Regards,

Sreenivasa