Hi,

I have a question from my customer for QSPI read timing.

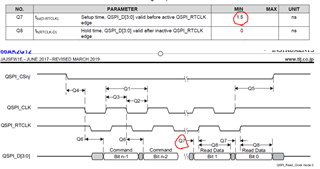

According to datasheet table 5-89, Read setup time is 1.5ns(min).

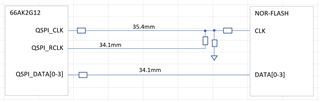

The customer uses QSPI_CLK=96MHz and their Flash memory's "clock low to output valid" parameter is 0 to 6nsec.

So above setup time is not met.

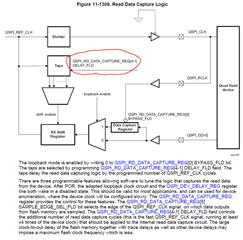

On the other hand, TRM Figure 11-1309 and Table 11-3212 mention QSPI_RD_DATA_CAPTURE_REG[4:1] DELAY_FLD.

It seems the read timing can be adjusted by this parameter using QSPI_REF_CLK which is running *4 QSPI_CLK (which is 384MHz).

Questions:

Q1) The read timing adjusted by DELAY_FLD bit is not visible at device IO boundary.

So it is OK to ignore the 1.5nsec setup time at IO boundary if data training results is OK?

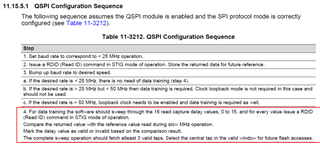

Q2) The configuration sequence says clock loopback should not be used if QSPI_CLK is <50MHz.

What is the reason clock loopback needs to be disabled?

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.