Part Number: SK-TDA4VM

Other Parts Discussed in Thread: TDA4VM

Hello TI.

I'm working on inferencing BlitzNet on TDA4 Board.

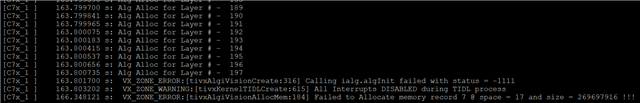

But I got a problem like this.

I checked the log about the Inferencing log under /opt/vx_app_arm_remote.log

Also, I found the similar Question in TI forum "Graph failed problem"

[reference link]

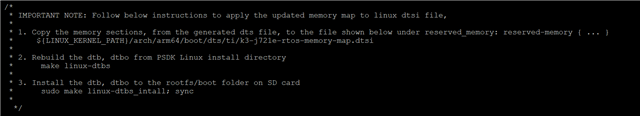

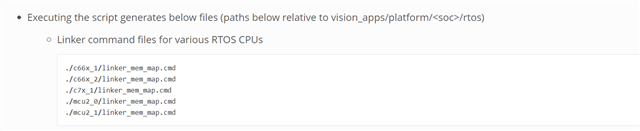

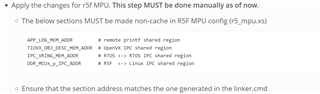

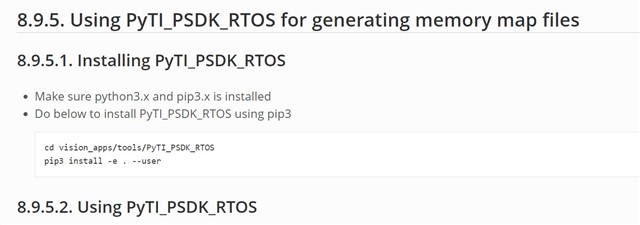

And I read that I should increase the memory size in DDR to accommodate these large requests. so I'm going to follow the next link

You mean that I have to follow the code from that link right?

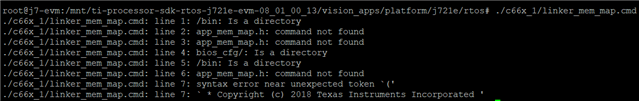

Board Environment : TDA4VM (ti-processor-sdk-rtos-j721e-evm-08_00_01_13)

Execution Path : /opt/tidl_test

ti-processor Path : /mnt/ti-processor-sdk-rtos-j721e-evm-08_00_01_13