Hi,

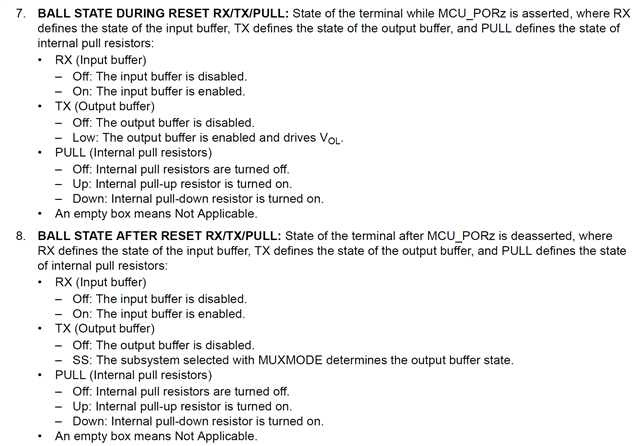

My customer wants to confirm about the hazard on the output signal at the power-on.

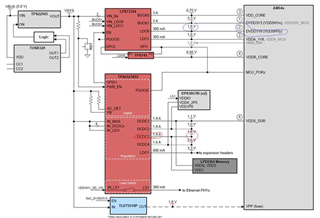

In their system, they’re selecting 1.8V on the VDDSHV * domain except some domain.

Is there any possibility to occur unintended hazard at the IO pins belonging to the 1.8V domain (for example, 1.8V SPI, 1.8V I2C or 1.8V GPMC pins connected to the external devices) even though the power was turned on according to the data sheet by using PMIC ?

In their system, there are some peripheral devices which have not yet powered on when AM64X is started are connected to AM64x , so it will be a problem if it receives a hazard. They want to confirm it just in case.

If a hazard occurs, they will have to review the peripheral circuits, so they are sorry, but they would appreciate it if they can receive an answer as early as possible. They hope today.

Regards,

Hideaki