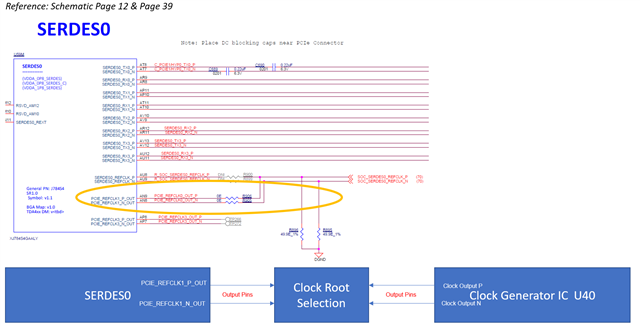

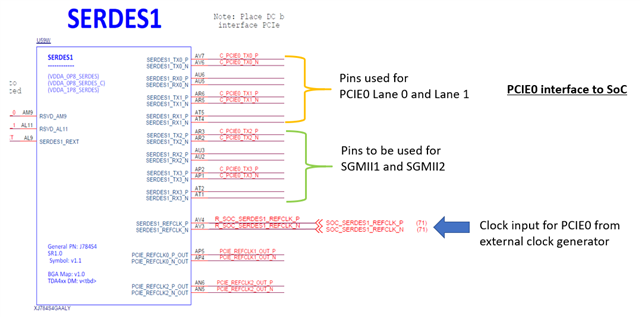

1. Why SERDES0_REFCLK is not used here in the below schematic?

2. PCIE_REFCLK1_OUT is connected to output of Clock generator IC. Both are Output Pins. Please clarify?

Reference Schematic: J784S4X Evaluation Board

Rev: E2

Ver: 3.1

File Name: PROC141E2(001)_SCH

Reference: Schematic Page 12 & Page 39