Part Number: TDA4VM

Hi,

We got the MIPI CSI issue on Linux system.

We connected mono camera (1280x720@30) on the tp2855 decoder that is a quad camera video decoder and it is stuck when streaming on.

And we checked the interrupt table that increase 2 interrupts on dma-controller chan1 when using yavta to capture video from camera.

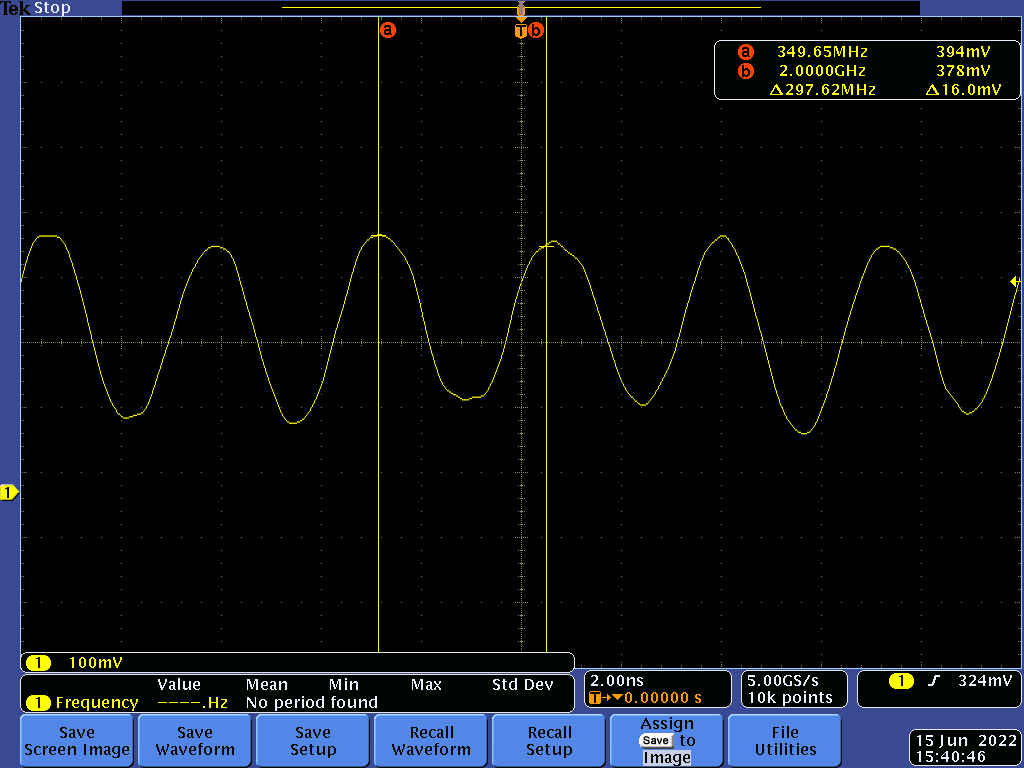

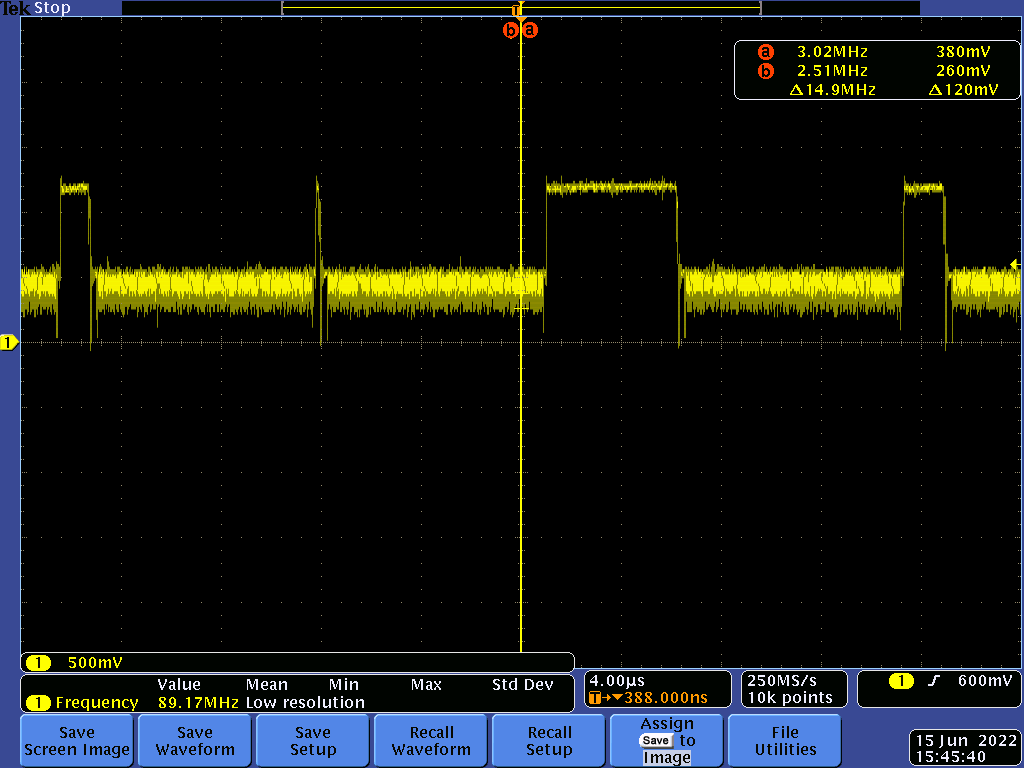

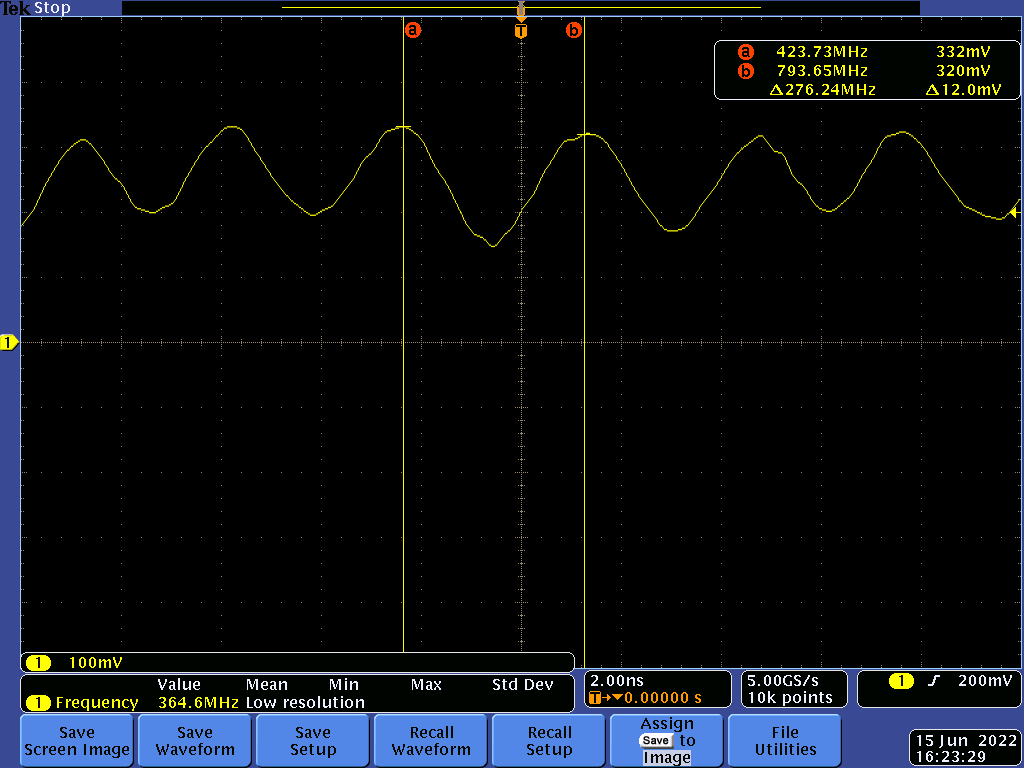

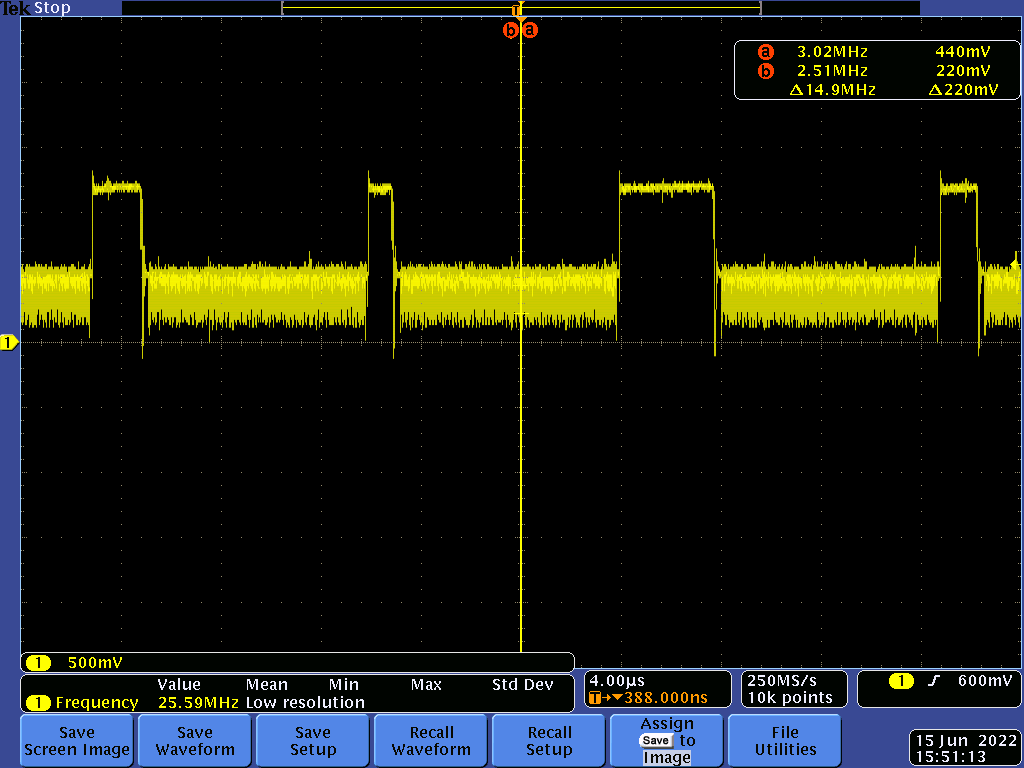

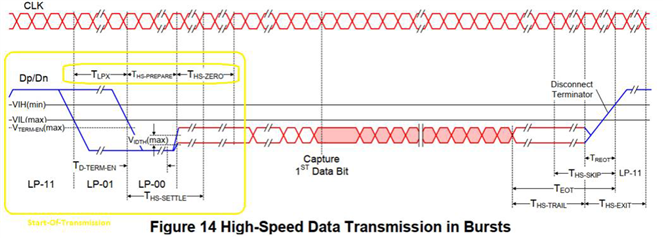

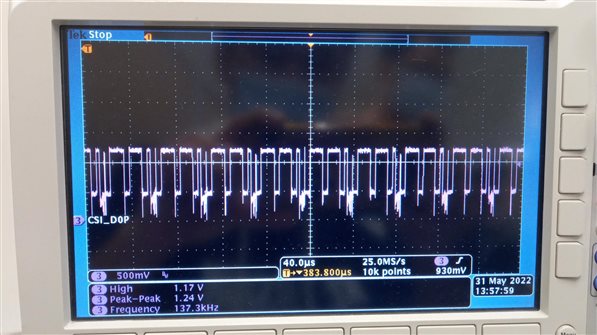

We measured the 2 pulse on MIPI clock and tp2855 send the MIPI data(D0-D3) always.

MIPI clock only got 2 pulse and the nothing else.

MIPI data

Which link frequency is correct when registering v4l2 control, V4L2_CID_LINK_FREQ?

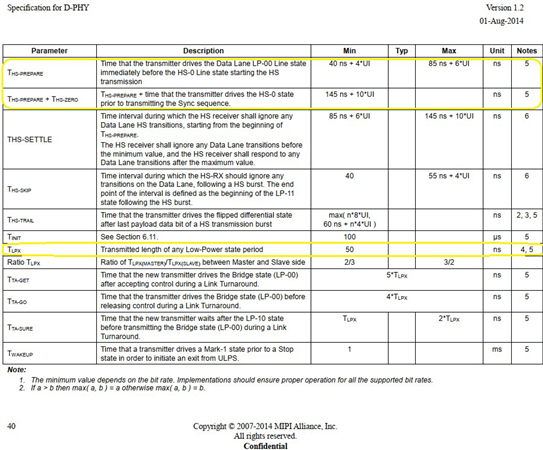

We trace the cadence csi2rx and mipi-dphy driver and know the hs_clk_rate is equal link frequency.

And research the following information from the Technical Reference Manual .

Is it meant to be maximum link frequency that is 312.5MHz?

Is CSI_RX_BYTE_CLK equal to MIPI clock?

We calculated the 720p@30 MIPI clock is

1650(V total) * 750(H total) * 30fps * 16bit(YUYV) / 4 lane / 2 = 74.25MHz

But the tp2855 clock lane frequency support is the following table.

We tried to set up link frequency is 297M or 594M and the streaming still stuck.

How do we figure out the problem?

Our product should be supported quad cameras on Linux system, but we know Linux platform will be supported multiple cameras on September from TI FAE and the following E2E thread . We currently use the version is 08.01.00.07.

Could you provide the multiple cameras patch to figure out the problem ASAP?