Hi,

My customer is designing their PCB and referring below document.

https://www.ti.com/lit/ug/spruiy5a/spruiy5a.pdf

In section 5, there is below description;

"The transmit pair should be routed away from the SoC on the top layer leaving a gap without blocking vias."

Customer understood this means TX signals should be routed on other layer than the top layer where the SoC is.

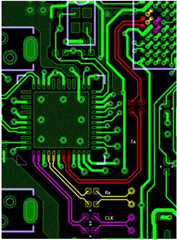

But Figure 5-1 shows TX signals are routed on the top layer (the same layer where the SoC is).

Is the description wrong?

Currently TX, RX and CLK are all routed on the top layer in customer's PCB design.

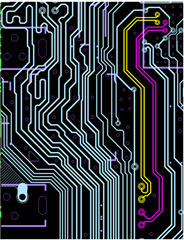

They are planning to move RX and CLK signals to other layers as same as Figure 5-1.

Do you have any recommendation?

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.