Part Number: TDA4VM

Please see attachment.

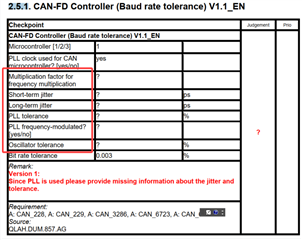

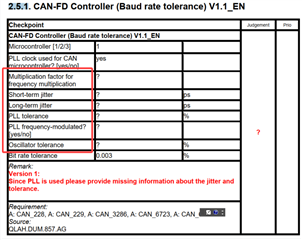

Did you know these performance parameters?

Please tell us how to fill it?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TDA4VM

Please see attachment.

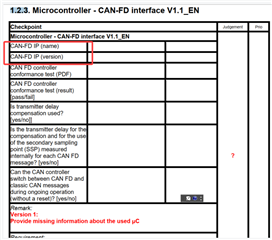

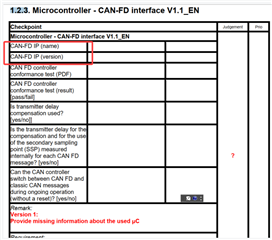

Did you know these performance parameters?

Please tell us how to fill it?

Closing this thread. It is the same as https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1110778/tda4vm-the-can-fd-controller-performance-form-fill

Sorry that was a glitch in the system. I have asked my colleague to take a look at this question.

Can you clarify what you mean by IP name and version number? The rest of your questions are properties of the PLL. You have a choice of the following PLLs for the MCAN functional clock: MCU_PLL2_HSDIV3 and MCU_PLL1_HSDIV2 for an MCU_MCAN interface, or PLL0_HSDIV4 for a Main MCAN interface. I will try to find the specs for those PLLs.

1.CAN IP is the name of the manufacturer's CAN FD architecture, such as MCU IP is R5F.

2.We are using MCU_MCAN_0, his clock source is MCU_PLL2_HSDIV3_CLKOUT.

3.How to know if a PLL is frequency modulated?

And the other questions on the picture need to clarify,Please tell us if you know.

The CAN has a mux that allows different PLL sources. I have measured the PLL configured to run at 2GHz and divided down to an 80MHz clock for the CAN. The procedure was to measure the PLL's period and then use the standard deviation of the distribution to define the jitter.

Jitter has a peculiar characteristic. As you measure over longer durations, the absolute value of the jitter increases but the percentage of the period decreases. That is reflected in the table shown below:

I have treated the short-term jitter as the jitter associated with 1 80MHz time-quanta.

I have treated the long term jitter as the jitter associated with 5 or 10 bit times (based upon reading Robustness of a CAN FD Bus System – About Oscillator Tolerance and Edge Deviations by Arthur Mutter); and without knowing what bit rate you are using, I have bounded the jitter by looking at 1Mbps and 8Mbps.

Short Term Jitter:

|

|

Period [ns] |

Std Dev [ps] |

3-sigma |

6-sigma |

|

80MHz TQ |

12.5 |

8.327 |

100.20% |

100.40% |

|

99.80% |

99.60% |

Long Term Jitter:

|

|

Period [ns] |

Std Dev [ps] |

3-sigma |

6-sigma |

|

5 bits @ 8Mbps |

625 |

16.055 |

100.008% |

100.015% |

|

99.992% |

99.985% |

|||

|

10 bits @ 8Mbps |

1250 |

20.207 |

100.005% |

100.010% |

|

99.995% |

99.990% |

|||

|

5 bits @ 1Mbps |

5000 |

19.784 |

100.001% |

100.002% |

|

99.999% |

99.998% |

|||

|

10 bits @ 1Mbps |

10000 |

25.095 |

100.001% |

100.002% |

|

99.999% |

99.998% |

Kevin

Also, the PLL can be modulated but whether it is modulated and the depth / frequency is programmable and your decision.

Kevin