Other Parts Discussed in Thread: DRA829

Hi Experts,

I am working on a DRA829 custome board with DS90UB941AS connecting to UB948 with 1080x1920 panel.

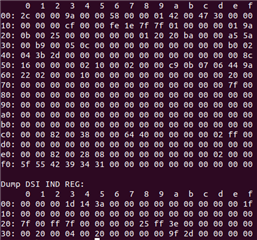

By following up the bring-up guide, I am stucked in “DSI_DTYPE Reported Wrongly”.

DSI_DTYPE retuens 0x0.

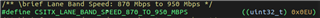

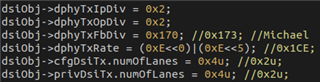

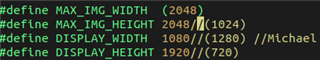

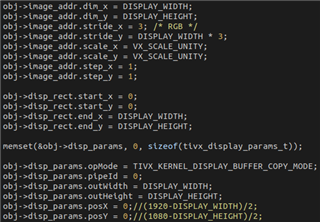

This is the configuration of DSI (4 lane): SDK 8.01

1. vision_apps/apps/basic_demos/app_tirtos/common/app_init.c

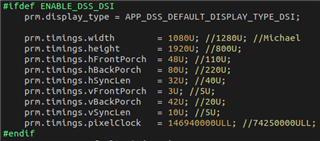

2. vision_apps/utils/dss/src/app_dss_defaults.c

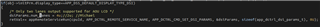

3. ti/drv/dss/src/drv/dctrl/dss_dctrlDsi.c

4. vision_apps/platform/j721e/rtos/common/app_cfg_mcu2_0.h

#undef ENABLE_CSI2TX

#undef ENABLE_DSS_EDP

#define ENABLE_DSS_DSI

5. vision_apps/apps/dl_demos/app_tidl/app_common.h

6. vision_apps/apps/dl_demos/app_tidl/main.c

7. DS90UB941AS Config:

uint8_t Ub941Ub925Config[][4] = {

#if 1

{0x16, 0x01, 0x02, 0x60},//Disable DSI

{0x16, 0x01, 0x08, 0x5},//Reset Reg

#endif

{0x16, 0x06, 0x00, 0x5},

{0x16, 0x1E, 0x01, 0x5},//Select port0

{0x16, 0x4F, 0x8C, 0x5},//DSI Continuous CLK/4 Lanes

{0x16, 0x5B, 0x0B, 0x5},//Dual mode "MUST"

{0x16, 0x03, 0x9A, 0x5},//I2C pass through

{0x2C, 0x1E, 0x30, 0x5},

{0x2C, 0x20, 0x03, 0x5},

0x16, 0x66, 0 , 0x5},

{0x16, 0x67, 0x0 , 0x5},

{0x16, 0x66, 1 , 0x5},

{0x16, 0x67, 0x0 , 0x5},

{0x16, 0x66, 2 , 0x5},

{0x16, 0x67, 0x0 , 0x5},

{0x16, 0x66, 3 , 0x5},

{0x16, 0x67, 0x16, 0x5},

{0x16, 0x66, 4 , 0x5},

{0x16, 0x67, 0xd8, 0x5},

{0x16, 0x66, 5 , 0x5},

{0x16, 0x67, 0x74, 0x5},

{0x16, 0x66, 6 , 0x5},

{0x16, 0x67, 0x7b, 0x5},

{0x16, 0x66, 7 , 0x5},

{0x16, 0x67, 0x38, 0x5},

{0x16, 0x66, 8 , 0x5},

{0x16, 0x67, 0x04, 0x5},

{0x16, 0x66, 9 , 0x5},

{0x16, 0x67, 0x78, 0x5},

{0x16, 0x66, 10 , 0x5},

{0x16, 0x67, 0x20, 0x5},

{0x16, 0x66, 11 , 0x5},

{0x16, 0x67, 0x0a, 0x5},

{0x16, 0x66, 12 , 0x5},

{0x16, 0x67, 0x50, 0x5},

{0x16, 0x66, 13 , 0x5},

{0x16, 0x67, 0x2a, 0x5},

{0x16, 0x66, 14 , 0x5},

{0x16, 0x67, 0x3 , 0x5},

{0x16, 0x66, 15 , 0x5},

{0x16, 0x67, 0x1e, 0x5},

{0x16, 0x66, 16 , 0x5},

{0x16, 0x67, 0xe , 0x5},

{0x16, 0x66, 17 , 0x5},

{0x16, 0x67, 0x21, 0x5},

{0x16, 0x66, 18 , 0x5},

{0x16, 0x67, 0x43, 0x5},

{0x16, 0x66, 19 , 0x5},

{0x16, 0x67, 0x65, 0x5},

{0x16, 0x66, 20 , 0x5},

{0x16, 0x67, 0x87, 0x5},

{0x16, 0x66, 21 , 0x5},

{0x16, 0x67, 0xa9, 0x5},

{0x16, 0x66, 22 , 0x5},

{0x16, 0x67, 0xcb, 0x5},

{0x16, 0x66, 23 , 0x5},

{0x16, 0x67, 0xed, 0x5},

{0x16, 0x66, 24 , 0x5},

{0x16, 0x67, 0xf , 0x5},

{0x16, 0x66, 25 , 0x5},

{0x16, 0x67, 0x0 , 0x5},

{0x16, 0x66, 26 , 0x5},

{0x16, 0x67, 0x04, 0x5},

#if 1

{0x16, 0x01, 0x00, 0x5},

#endif

#if 0

{0x16, 0x65, 0x68, 0x5},

{0x16, 0x64, 0x15, 0xF8},

#endif

};

8. Output:

root@j7-evm:/opt/vision_apps# [MCU2_0] 3.618258 s: CIO: Init ... Done !!!

[MCU2_0] 3.618335 s: ### CPU Frequency = 1000000000 Hz

[MCU2_0] 3.618379 s: APP: Init ... !!!

[MCU2_0] 3.618405 s: SCICLIENT: Init ... !!!

[MCU2_0] 3.618666 s: SCICLIENT: DMSC FW version [21.9.1--v2021.09a (Terrific Lla]

[MCU2_0] 3.618724 s: SCICLIENT: DMSC FW revision 0x15

[MCU2_0] 3.618780 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_0] 3.618821 s: SCICLIENT: Init ... Done !!!

[MCU2_0] 3.618851 s: UDMA: Init ... !!!

[MCU2_0] 3.620276 s: UDMA: Init ... Done !!!

[MCU2_0] 3.620347 s: MEM: Init ... !!!

[MCU2_0] 3.620397 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ d9000000 of size 16777216 bytes !!!

[MCU2_0] 3.620480 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 3600000 of size 262144 bytes !!!

[MCU2_0] 3.620544 s: MEM: Init ... Done !!!

[MCU2_0] 3.620573 s: IPC: Init ... !!!

[MCU2_0] 3.620642 s: IPC: 6 CPUs participating in IPC !!!

[MCU2_0] 3.620689 s: IPC: Waiting for HLOS to be ready ... !!!

[MCU2_0] 17.746026 s: IPC: HLOS is ready !!!

[MCU2_0] 17.761773 s: IPC: Init ... Done !!!

[MCU2_0] 17.761843 s: APP: Syncing with 5 CPUs ... !!!

[MCU2_0] 17.927250 s: APP: Syncing with 5 CPUs ... Done !!!

[MCU2_0] 17.927488 s: REMOTE_SERVICE: Init ... !!!

[MCU2_0] 17.929049 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_0] 17.929123 s: FVID2: Init ... !!!

[MCU2_0] 17.929204 s: FVID2: Init ... Done !!!

[MCU2_0] 17.929256 s: DSS: Init ... !!!

[MCU2_0] 17.929287 s: DSS: Display type is DSI !!!

[MCU2_0] 17.929316 s: DSS: M2M Path is enabled !!!

[MCU2_0] 17.929345 s: DSS: SoC init ... !!!

[MCU2_0] 17.929373 s: SCICLIENT: Sciclient_pmSetModuleState module=152 state=2

[MCU2_0] 17.929551 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 17.929596 s: SCICLIENT: Sciclient_pmSetModuleState module=150 state=2

[MCU2_0] 17.930095 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 17.930138 s: SCICLIENT: Sciclient_pmSetModuleState module=296 state=2

[MCU2_0] 17.930530 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 17.930572 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=9 parent=11

[MCU2_0] 17.931114 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 17.931157 s: SCICLIENT: Sciclient_pmSetModuleClkFreq module=152 clk=9 freq=146940000

[MCU2_0] 17.932472 s: SCICLIENT: Sciclient_pmSetModuleClkFreq success

[MCU2_0] 17.932514 s: SCICLIENT: Sciclient_pmModuleClkRequest module=152 clk=9 state=2 flag=0

[MCU2_0] 17.933070 s: SCICLIENT: Sciclient_pmModuleClkRequest success

[MCU2_0] 17.933111 s: DSS: SoC init ... Done !!!

[MCU2_0] 17.933142 s: DSS: Configuring SERDES ... !!!

[MCU2_0] 18.074743 s: 0x2c Success!!

[MCU2_0] 18.079738 s: 0x2c Success!!

[MCU2_0] 18.612735 s: I2c finish

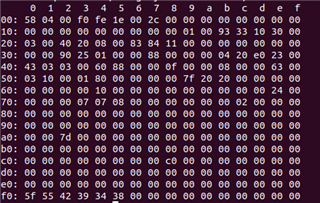

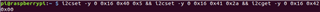

[MCU2_0] 18.612940 s: [Michael] 0x16, 0x0 0x2c

[MCU2_0] 18.613139 s: [Michael] 0x16, 0x1 0x0

[MCU2_0] 18.613323 s: [Michael] 0x16, 0x2 0x0

[MCU2_0] 18.613507 s: [Michael] 0x16, 0x3 0x9a

[MCU2_0] 18.613691 s: [Michael] 0x16, 0x4 0x0

[MCU2_0] 18.613881 s: [Michael] 0x16, 0x5 0x0

[MCU2_0] 18.614070 s: [Michael] 0x16, 0x6 0x58

[MCU2_0] 18.614260 s: [Michael] 0x16, 0x7 0x0

[MCU2_0] 18.614444 s: [Michael] 0x16, 0x8 0x0

[MCU2_0] 18.614625 s: [Michael] 0x16, 0x9 0x1

[MCU2_0] 18.614812 s: [Michael] 0x16, 0xa 0x81

[MCU2_0] 18.615003 s: [Michael] 0x16, 0xb 0x0

[MCU2_0] 18.615185 s: [Michael] 0x16, 0xc 0x7

[MCU2_0] 18.615369 s: [Michael] 0x16, 0xd 0x30

[MCU2_0] 18.615554 s: [Michael] 0x16, 0xe 0x0

[MCU2_0] 18.615745 s: [Michael] 0x16, 0xf 0x0

[MCU2_0] 18.615930 s: [Michael] 0x16, 0x10 0x0

[MCU2_0] 18.616118 s: [Michael] 0x16, 0x11 0x0

[MCU2_0] 18.616303 s: [Michael] 0x16, 0x12 0x0

[MCU2_0] 18.616488 s: [Michael] 0x16, 0x13 0xcf

[MCU2_0] 18.616674 s: [Michael] 0x16, 0x14 0x0

[MCU2_0] 18.616860 s: [Michael] 0x16, 0x15 0x0

[MCU2_0] 18.617047 s: [Michael] 0x16, 0x16 0xfe

[MCU2_0] 18.617237 s: [Michael] 0x16, 0x17 0x1e

[MCU2_0] 18.617424 s: [Michael] 0x16, 0x18 0x7f

[MCU2_0] 18.617607 s: [Michael] 0x16, 0x19 0x7f

[MCU2_0] 18.617800 s: [Michael] 0x16, 0x1a 0x1

[MCU2_0] 18.617988 s: [Michael] 0x16, 0x1b 0x0

[MCU2_0] 18.618175 s: [Michael] 0x16, 0x1c 0x0

[MCU2_0] 18.618357 s: [Michael] 0x16, 0x1d 0x0

[MCU2_0] 18.618541 s: [Michael] 0x16, 0x1e 0x1

[MCU2_0] 18.618726 s: [Michael] 0x16, 0x1f 0x0

[MCU2_0] 18.618920 s: [Michael] 0x16, 0x20 0xb

[MCU2_0] 18.619109 s: [Michael] 0x16, 0x21 0x0

[MCU2_0] 18.619291 s: [Michael] 0x16, 0x22 0x25

[MCU2_0] 18.619475 s: [Michael] 0x16, 0x23 0x0

[MCU2_0] 18.619657 s: [Michael] 0x16, 0x24 0x0

[MCU2_0] 18.619846 s: [Michael] 0x16, 0x25 0x0

[MCU2_0] 18.620032 s: [Michael] 0x16, 0x26 0x0

[MCU2_0] 18.620219 s: [Michael] 0x16, 0x27 0x0

[MCU2_0] 18.620403 s: [Michael] 0x16, 0x28 0x1

[MCU2_0] 18.620586 s: [Michael] 0x16, 0x29 0x20

[MCU2_0] 18.620775 s: [Michael] 0x16, 0x2a 0x20

[MCU2_0] 18.620962 s: [Michael] 0x16, 0x2b 0xa0

[MCU2_0] 18.621149 s: [Michael] 0x16, 0x2c 0x0

[MCU2_0] 18.621332 s: [Michael] 0x16, 0x2d 0x0

[MCU2_0] 18.621517 s: [Michael] 0x16, 0x2e 0xa5

[MCU2_0] 18.621699 s: [Michael] 0x16, 0x2f 0x5a

[MCU2_0] 18.621890 s: [Michael] 0x16, 0x30 0x0

[MCU2_0] 18.622076 s: [Michael] 0x16, 0x31 0xb9

[MCU2_0] 18.622258 s: [Michael] 0x16, 0x32 0x0

[MCU2_0] 18.622439 s: [Michael] 0x16, 0x33 0x5

[MCU2_0] 18.622625 s: [Michael] 0x16, 0x34 0xc

[MCU2_0] 18.622821 s: [Michael] 0x16, 0x35 0x0

[MCU2_0] 18.623011 s: [Michael] 0x16, 0x36 0x0

[MCU2_0] 18.623197 s: [Michael] 0x16, 0x37 0x0

[MCU2_0] 18.623383 s: [Michael] 0x16, 0x38 0x0

[MCU2_0] 18.623569 s: [Michael] 0x16, 0x39 0x0

[MCU2_0] 18.623762 s: [Michael] 0x16, 0x3a 0x0

[MCU2_0] 18.623951 s: [Michael] 0x16, 0x3b 0x0

[MCU2_0] 18.624139 s: [Michael] 0x16, 0x3c 0x0

[MCU2_0] 18.624321 s: [Michael] 0x16, 0x3d 0x0

[MCU2_0] 18.624504 s: [Michael] 0x16, 0x3e 0xb0

[MCU2_0] 18.624686 s: [Michael] 0x16, 0x3f 0x2

[MCU2_0] 18.624875 s: [Michael] 0x16, 0x40 0x10

[MCU2_0] 18.625063 s: [Michael] 0x16, 0x41 0x94

[MCU2_0] 18.625246 s: [Michael] 0x16, 0x42 0x0

[MCU2_0] 18.625423 s: [Michael] 0x16, 0x43 0x0

[MCU2_0] 18.625605 s: [Michael] 0x16, 0x44 0x0

[MCU2_0] 18.625794 s: [Michael] 0x16, 0x45 0x0

[MCU2_0] 18.625982 s: [Michael] 0x16, 0x46 0x0

[MCU2_0] 18.626165 s: [Michael] 0x16, 0x47 0x0

[MCU2_0] 18.626351 s: [Michael] 0x16, 0x48 0x0

[MCU2_0] 18.626531 s: [Michael] 0x16, 0x49 0x0

[MCU2_0] 18.626717 s: [Michael] 0x16, 0x4a 0x0

[MCU2_0] 18.626912 s: [Michael] 0x16, 0x4b 0x0

[MCU2_0] 18.627095 s: [Michael] 0x16, 0x4c 0x0

[MCU2_0] 18.627279 s: [Michael] 0x16, 0x4d 0x0

[MCU2_0] 18.627463 s: [Michael] 0x16, 0x4e 0x0

[MCU2_0] 18.627644 s: [Michael] 0x16, 0x4f 0x8c

[MCU2_0] 18.627834 s: [Michael] 0x16, 0x50 0x16

[MCU2_0] 18.628023 s: [Michael] 0x16, 0x51 0x0

[MCU2_0] 18.628213 s: [Michael] 0x16, 0x52 0x0

[MCU2_0] 18.628399 s: [Michael] 0x16, 0x53 0x0

[MCU2_0] 18.628583 s: [Michael] 0x16, 0x54 0x2

[MCU2_0] 18.628769 s: [Michael] 0x16, 0x55 0x10

[MCU2_0] 18.628954 s: [Michael] 0x16, 0x56 0x0

[MCU2_0] 18.629143 s: [Michael] 0x16, 0x57 0x2

[MCU2_0] 18.629324 s: [Michael] 0x16, 0x58 0x0

[MCU2_0] 18.629509 s: [Michael] 0x16, 0x59 0x0

[MCU2_0] 18.629693 s: [Michael] 0x16, 0x5a 0x18

[MCU2_0] 18.629885 s: [Michael] 0x16, 0x5b 0xb

[MCU2_0] 18.630074 s: [Michael] 0x16, 0x5c 0x7

[MCU2_0] 18.630262 s: [Michael] 0x16, 0x5d 0x6

[MCU2_0] 18.630446 s: [Michael] 0x16, 0x5e 0x44

[MCU2_0] 18.630628 s: [Michael] 0x16, 0x5f 0x17

[MCU2_0] 18.630821 s: [Michael] 0x16, 0x60 0x22

[MCU2_0] 18.631007 s: [Michael] 0x16, 0x61 0x2

[MCU2_0] 18.631195 s: [Michael] 0x16, 0x62 0x0

[MCU2_0] 18.631378 s: [Michael] 0x16, 0x63 0x0

[MCU2_0] 18.631562 s: [Michael] 0x16, 0x64 0x15

[MCU2_0] 18.631755 s: [Michael] 0x16, 0x65 0x6c

[MCU2_0] 18.631945 s: [Michael] 0x16, 0x66 0x1a

[MCU2_0] 18.632134 s: [Michael] 0x16, 0x67 0x4

[MCU2_0] 18.632318 s: [Michael] 0x16, 0x68 0x0

[MCU2_0] 18.632506 s: [Michael] 0x16, 0x69 0x0

[MCU2_0] 18.632692 s: [Michael] 0x16, 0x6a 0x0

[MCU2_0] 18.632891 s: [Michael] 0x16, 0x6b 0x0

[MCU2_0] 18.633078 s: [Michael] 0x16, 0x6c 0x0

[MCU2_0] 18.633264 s: [Michael] 0x16, 0x6d 0x0

[MCU2_0] 18.633447 s: [Michael] 0x16, 0x6e 0x20

[MCU2_0] 18.633630 s: [Michael] 0x16, 0x6f 0x0

[MCU2_0] 18.633821 s: [Michael] 0x16, 0x70 0x0

[MCU2_0] 18.634006 s: [Michael] 0x16, 0x71 0x0

[MCU2_0] 18.634194 s: [Michael] 0x16, 0x72 0x0

[MCU2_0] 18.634378 s: [Michael] 0x16, 0x73 0x0

[MCU2_0] 18.634559 s: [Michael] 0x16, 0x74 0x0

[MCU2_0] 18.634750 s: [Michael] 0x16, 0x75 0x0

[MCU2_0] 18.634938 s: [Michael] 0x16, 0x76 0x0

[MCU2_0] 18.635124 s: [Michael] 0x16, 0x77 0x0

[MCU2_0] 18.635307 s: [Michael] 0x16, 0x78 0x0

[MCU2_0] 18.635494 s: [Michael] 0x16, 0x79 0x0

[MCU2_0] 18.635677 s: [Michael] 0x16, 0x7a 0x0

[MCU2_0] 18.635866 s: [Michael] 0x16, 0x7b 0x0

[MCU2_0] 18.636053 s: [Michael] 0x16, 0x7c 0x0

[MCU2_0] 18.636238 s: [Michael] 0x16, 0x7d 0x0

[MCU2_0] 18.636423 s: [Michael] 0x16, 0x7e 0x7f

[MCU2_0] 18.636604 s: [Michael] 0x16, 0x7f 0x0

[MCU2_0] 18.636640 s: DSS: SERDES Configuration... Done !!!

[MCU2_0] 18.639860 s: DSS: Init ... Done !!!

[MCU2_0] 18.639933 s: [Michael] prm.timings.width = 1080

[MCU2_0] 18.639976 s: [Michael] prm.timings.height = 1920

[MCU2_0] 18.640011 s: VHWA: VPAC Init ... !!!

[MCU2_0] 18.640037 s: SCICLIENT: Sciclient_pmSetModuleState module=290 state=2

[MCU2_0] 18.640225 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 18.640271 s: VHWA: LDC Init ... !!!

[MCU2_0] 18.643867 s: VHWA: LDC Init ... Done !!!

[MCU2_0] 18.643934 s: VHWA: MSC Init ... !!!

[MCU2_0] 18.654637 s: VHWA: MSC Init ... Done !!!

[MCU2_0] 18.654701 s: VHWA: NF Init ... !!!

[MCU2_0] 18.656612 s: VHWA: NF Init ... Done !!!

[MCU2_0] 18.656679 s: VHWA: VISS Init ... !!!

[MCU2_0] 18.667769 s: VHWA: VISS Init ... Done !!!

[MCU2_0] 18.667839 s: VHWA: VPAC Init ... Done !!!

[MCU2_0] 18.667893 s: VX_ZONE_INIT:Enabled

[MCU2_0] 18.667924 s: VX_ZONE_ERROR:Enabled

[MCU2_0] 18.667952 s: VX_ZONE_WARNING:Enabled

[MCU2_0] 18.669135 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target IPU1-0

[MCU2_0] 18.669375 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target VPAC_NF

[MCU2_0] 18.669606 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target VPAC_LDC1

[MCU2_0] 18.669845 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target VPAC_MSC1

[MCU2_0] 18.670077 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target VPAC_MSC2

[MCU2_0] 18.670385 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target VPAC_VISS1

[MCU2_0] 18.670652 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE1

[MCU2_0] 18.670928 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE2

[MCU2_0] 18.671189 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DISPLAY1

[MCU2_0] 18.671454 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DISPLAY2

[MCU2_0] 18.671685 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CSITX

[MCU2_0] 18.671971 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE3

[MCU2_0] 18.672240 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE4

[MCU2_0] 18.672509 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE5

[MCU2_0] 18.672779 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE6

[MCU2_0] 18.673086 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE7

[MCU2_0] 18.673397 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target CAPTURE8

[MCU2_0] 18.673645 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DSS_M2M1

[MCU2_0] 18.673891 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DSS_M2M2

[MCU2_0] 18.674126 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DSS_M2M3

[MCU2_0] 18.674357 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DSS_M2M4

[MCU2_0] 18.674415 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[MCU2_0] 18.674455 s: APP: OpenVX Target kernel init ... !!!

[MCU2_0] 18.689902 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_0] 18.689969 s: CSI2RX: Init ... !!!

[MCU2_0] 18.690001 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2

[MCU2_0] 18.690146 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 18.690196 s: SCICLIENT: Sciclient_pmSetModuleState module=26 state=2

[MCU2_0] 18.690355 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 18.690396 s: SCICLIENT: Sciclient_pmSetModuleState module=27 state=2

[MCU2_0] 18.690539 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 18.690579 s: SCICLIENT: Sciclient_pmSetModuleState module=147 state=2

[MCU2_0] 18.690684 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 18.690723 s: SCICLIENT: Sciclient_pmSetModuleState module=148 state=2

[MCU2_0] 18.690836 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 18.691631 s: CSI2RX: Init ... Done !!!

[MCU2_0] 18.691694 s: ISS: Init ... !!!

[MCU2_0] 18.691757 s: Michael: IssSensor_IMX390_Init()

[MCU2_0] 18.691797 s: Found sensor IMX390-UB953_D3 at location 0

[MCU2_0] 18.691845 s: Found sensor AR0233-UB953_MARS at location 1

[MCU2_0] 18.691888 s: Found sensor AR0820-UB953_LI at location 2

[MCU2_0] 18.691930 s: Found sensor UB9xxx_RAW12_TESTPATTERN at location 3

[MCU2_0] 18.691971 s: Found sensor UB96x_UYVY_TESTPATTERN at location 4

[MCU2_0] 18.692010 s: Found sensor GW_AR0233_UYVY at location 5

[MCU2_0] 18.692051 s: Michael: IssSensor_ISX019_Init()

[MCU2_0] 18.692080 s: Found sensor ISX019-UB913_oTo at location 6

[MCU2_0] 18.692119 s: IssSensor_Init ... Done !!!

[MCU2_0] 18.692212 s: vissRemoteServer_Init ... Done !!!

[MCU2_0] 18.692282 s: IttRemoteServer_Init ... Done !!!

[MCU2_0] 18.692319 s: UDMA Copy: Init ... !!!

[MCU2_0] 18.694238 s: UDMA Copy: Init ... Done !!!

[MCU2_0] 18.694345 s: APP: Init ... Done !!!

[MCU2_0] 18.694384 s: APP: Run ... !!!

[MCU2_0] 18.694412 s: IPC: Starting echo test ...

[MCU2_0] 18.696988 s: APP: Run ... Done !!!

[MCU2_0] 18.698582 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[.] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU2_0] 18.698912 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU2_0] 18.699031 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU2_0] 18.699135 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU2_1] 3.633229 s: CIO: Init ... Done !!!

[MCU2_1] 3.633298 s: ### CPU Frequency = 1000000000 Hz

[MCU2_1] 3.633342 s: APP: Init ... !!!

[MCU2_1] 3.633367 s: SCICLIENT: Init ... !!!

[MCU2_1] 3.633623 s: SCICLIENT: DMSC FW version [21.9.1--v2021.09a (Terrific Lla]

[MCU2_1] 3.633675 s: SCICLIENT: DMSC FW revision 0x15

[MCU2_1] 3.633710 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_1] 3.633747 s: SCICLIENT: Init ... Done !!!

[MCU2_1] 3.633793 s: UDMA: Init ... !!!

[MCU2_1] 3.635301 s: UDMA: Init ... Done !!!

[MCU2_1] 3.635367 s: MEM: Init ... !!!

[MCU2_1] 3.635414 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ da000000 of size 16777216 bytes !!!

[MCU2_1] 3.635489 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 3640000 of size 262144 bytes !!!

[MCU2_1] 3.635550 s: MEM: Init ... Done !!!

[MCU2_1] 3.635576 s: IPC: Init ... !!!

[MCU2_1] 3.635638 s: IPC: 6 CPUs participating in IPC !!!

[MCU2_1] 3.635693 s: IPC: Waiting for HLOS to be ready ... !!!

[MCU2_1] 17.911420 s: IPC: HLOS is ready !!!

[MCU2_1] 17.927134 s: IPC: Init ... Done !!!

[MCU2_1] 17.927201 s: APP: Syncing with 5 CPUs ... !!!

[MCU2_1] 17.927248 s: APP: Syncing with 5 CPUs ... Done !!!

[MCU2_1] 17.927287 s: REMOTE_SERVICE: Init ... !!!

[MCU2_1] 17.929058 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_1] 17.929129 s: FVID2: Init ... !!!

[MCU2_1] 17.929205 s: FVID2: Init ... Done !!!

[MCU2_1] 17.929239 s: VHWA: DMPAC: Init ... !!!

[MCU2_1] 17.929266 s: SCICLIENT: Sciclient_pmSetModuleState module=48 state=2

[MCU2_1] 17.929452 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 17.929496 s: SCICLIENT: Sciclient_pmSetModuleState module=305 state=2

[MCU2_1] 17.930013 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 17.930055 s: VHWA: DOF Init ... !!!

[MCU2_1] 17.940173 s: VHWA: DOF Init ... Done !!!

[MCU2_1] 17.940239 s: VHWA: SDE Init ... !!!

[MCU2_1] 17.943139 s: VHWA: SDE Init ... Done !!!

[MCU2_1] 17.943199 s: VHWA: DMPAC: Init ... Done !!!

[MCU2_1] 17.943250 s: VX_ZONE_INIT:Enabled

[MCU2_1] 17.943284 s: VX_ZONE_ERROR:Enabled

[MCU2_1] 17.943312 s: VX_ZONE_WARNING:Enabled

[MCU2_1] 17.944484 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DMPAC_SDE

[MCU2_1] 17.944723 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target DMPAC_DOF

[MCU2_1] 17.944962 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:54] Added target IPU1-1

[MCU2_1] 17.945019 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[MCU2_1] 17.945058 s: APP: OpenVX Target kernel init ... !!!

[MCU2_1] 17.945343 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_1] 17.945384 s: UDMA Copy: Init ... !!!

[MCU2_1] 17.947305 s: UDMA Copy: Init ... Done !!!

[MCU2_1] 17.947377 s: APP: Init ... Done !!!

[MCU2_1] 17.947415 s: APP: Run ... !!!

[MCU2_1] 17.947441 s: IPC: Starting echo test ...

[MCU2_1] 17.949994 s: APP: Run ... Done !!!

[MCU2_1] 17.951418 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU2_1] 17.951543 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU2_1] 17.951642 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU2_1] 18.698536 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[P]

[C6x_1 ] 3.703249 s: CIO: Init ... Done !!!

[C6x_1 ] 3.703278 s: ### CPU Frequency = 1350000000 Hz

[C6x_1 ] 3.703289 s: APP: Init ... !!!

[C6x_1 ] 3.703298 s: SCICLIENT: Init ... !!!

[C6x_1 ] 3.703553 s: SCICLIENT: DMSC FW version [21.9.1--v2021.09a (Terrific Lla]

[C6x_1 ] 3.703569 s: SCICLIENT: DMSC FW revision 0x15

[C6x_1 ] 3.703579 s: SCICLIENT: DMSC FW ABI revision 3.1

[C6x_1 ] 3.703590 s: SCICLIENT: Init ... Done !!!

[C6x_1 ] 3.703600 s: UDMA: Init ... !!!

[C6x_1 ] 3.705374 s: UDMA: Init ... Done !!!

[C6x_1 ] 3.705398 s: MEM: Init ... !!!

[C6x_1 ] 3.705413 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ dc000000 of size 16777216 bytes !!!

[C6x_1 ] 3.705433 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!!

[C6x_1 ] 3.705450 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ dd000000 of size 50331648 bytes !!!

[C6x_1 ] 3.705468 s: MEM: Init ... Done !!!

[C6x_1 ] 3.705477 s: IPC: Init ... !!!

[C6x_1 ] 3.705501 s: IPC: 6 CPUs participating in IPC !!!

[C6x_1 ] 3.705517 s: IPC: Waiting for HLOS to be ready ... !!!

[C6x_1 ] 12.004874 s: IPC: HLOS is ready !!!

[C6x_1 ] 12.009516 s: IPC: Init ... Done !!!

[C6x_1 ] 12.009547 s: APP: Syncing with 5 CPUs ... !!!

[C6x_1 ] 17.927248 s: APP: Syncing with 5 CPUs ... Done !!!

[C6x_1 ] 17.927260 s: REMOTE_SERVICE: Init ... !!!

[C6x_1 ] 17.927934 s: REMOTE_SERVICE: Init ... Done !!!

[C6x_1 ] 17.927976 s: VX_ZONE_INIT:Enabled

[C6x_1 ] 17.927988 s: VX_ZONE_ERROR:Enabled

[C6x_1 ] 17.927999 s: VX_ZONE_WARNING:Enabled

[C6x_1 ] 17.928892 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[C6x_1 ] 17.928910 s: APP: OpenVX Target kernel init ... !!!

[C6x_1 ] 17.929346 s: APP: OpenVX Target kernel init ... Done !!!

[C6x_1 ] 17.929368 s: UDMA Copy: Init ... !!!

[C6x_1 ] 17.934153 s: UDMA Copy: Init ... Done !!!

[C6x_1 ] 17.934177 s: APP: Init ... Done !!!

[C6x_1 ] 17.934975 s: APP: Run ... !!!

[C6x_1 ] 17.934991 s: IPC: Starting echo test ...

[C6x_1 ] 17.936057 s: APP: Run ... Done !!!

[C6x_1 ] 17.936470 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[x] C7X_1[P]

[C6x_1 ] 17.936917 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 17.951117 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 18.698341 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_2 ] 3.794438 s: CIO: Init ... Done !!!

[C6x_2 ] 3.794468 s: ### CPU Frequency = 1350000000 Hz

[C6x_2 ] 3.794480 s: APP: Init ... !!!

[C6x_2 ] 3.794489 s: SCICLIENT: Init ... !!!

[C6x_2 ] 3.794740 s: SCICLIENT: DMSC FW version [21.9.1--v2021.09a (Terrific Lla]

[C6x_2 ] 3.794756 s: SCICLIENT: DMSC FW revision 0x15

[C6x_2 ] 3.794767 s: SCICLIENT: DMSC FW ABI revision 3.1

[C6x_2 ] 3.794778 s: SCICLIENT: Init ... Done !!!

[C6x_2 ] 3.794788 s: UDMA: Init ... !!!

[C6x_2 ] 3.796583 s: UDMA: Init ... Done !!!

[C6x_2 ] 3.796608 s: MEM: Init ... !!!

[C6x_2 ] 3.796623 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e0000000 of size 16777216 bytes !!!

[C6x_2 ] 3.796643 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!!

[C6x_2 ] 3.796660 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e1000000 of size 50331648 bytes !!!

[C6x_2 ] 3.796679 s: MEM: Init ... Done !!!

[C6x_2 ] 3.796688 s: IPC: Init ... !!!

[C6x_2 ] 3.796712 s: IPC: 6 CPUs participating in IPC !!!

[C6x_2 ] 3.796729 s: IPC: Waiting for HLOS to be ready ... !!!

[C6x_2 ] 12.212903 s: IPC: HLOS is ready !!!

[C6x_2 ] 12.217543 s: IPC: Init ... Done !!!

[C6x_2 ] 12.217574 s: APP: Syncing with 5 CPUs ... !!!

[C6x_2 ] 17.927248 s: APP: Syncing with 5 CPUs ... Done !!!

[C6x_2 ] 17.927261 s: REMOTE_SERVICE: Init ... !!!

[C6x_2 ] 17.927945 s: REMOTE_SERVICE: Init ... Done !!!

[C6x_2 ] 17.927987 s: VX_ZONE_INIT:Enabled

[C6x_2 ] 17.927999 s: VX_ZONE_ERROR:Enabled

[C6x_2 ] 17.928010 s: VX_ZONE_WARNING:Enabled

[C6x_2 ] 17.928899 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[C6x_2 ] 17.928916 s: APP: OpenVX Target kernel init ... !!!

[C6x_2 ] 17.929355 s: APP: OpenVX Target kernel init ... Done !!!

[C6x_2 ] 17.929376 s: UDMA Copy: Init ... !!!

[C6x_2 ] 17.934475 s: UDMA Copy: Init ... Done !!!

[C6x_2 ] 17.934499 s: APP: Init ... Done !!!

[C6x_2 ] 17.935304 s: APP: Run ... !!!

[C6x_2 ] 17.935320 s: IPC: Starting echo test ...

[C6x_2 ] 17.936478 s: APP: Run ... Done !!!

[C6x_2 ] 17.936919 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[s] C7X_1[.]

[C6x_2 ] 17.936964 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 17.951146 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 18.698375 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[s] C7X_1[P]

[C7x_1 ] 4.012493 s: CIO: Init ... Done !!!

[C7x_1 ] 4.012508 s: ### CPU Frequency = 1000000000 Hz

[C7x_1 ] 4.012520 s: APP: Init ... !!!

[C7x_1 ] 4.012529 s: SCICLIENT: Init ... !!!

[C7x_1 ] 4.012746 s: SCICLIENT: DMSC FW version [21.9.1--v2021.09a (Terrific Lla]

[C7x_1 ] 4.012761 s: SCICLIENT: DMSC FW revision 0x15

[C7x_1 ] 4.012772 s: SCICLIENT: DMSC FW ABI revision 3.1

[C7x_1 ] 4.012783 s: SCICLIENT: Init ... Done !!!

[C7x_1 ] 4.012792 s: UDMA: Init ... !!!

[C7x_1 ] 4.013981 s: UDMA: Init ... Done !!!

[C7x_1 ] 4.013994 s: MEM: Init ... !!!

[C7x_1 ] 4.014005 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ 100000000 of size 268435456 bytes !!!

[C7x_1 ] 4.014027 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 70020000 of size 8159232 bytes !!!

[C7x_1 ] 4.014045 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 64800000 of size 458752 bytes !!!

[C7x_1 ] 4.014063 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 64e00000 of size 16384 bytes !!!

[C7x_1 ] 4.014080 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e4000000 of size 402653184 bytes !!!

[C7x_1 ] 4.014100 s: MEM: Init ... Done !!!

[C7x_1 ] 4.014108 s: IPC: Init ... !!!

[C7x_1 ] 4.014123 s: IPC: 6 CPUs participating in IPC !!!

[C7x_1 ] 4.014138 s: IPC: Waiting for HLOS to be ready ... !!!

[C7x_1 ] 12.443410 s: IPC: HLOS is ready !!!

[C7x_1 ] 12.445532 s: IPC: Init ... Done !!!

[C7x_1 ] 12.445548 s: APP: Syncing with 5 CPUs ... !!!

[C7x_1 ] 17.927249 s: APP: Syncing with 5 CPUs ... Done !!!

[C7x_1 ] 17.927266 s: REMOTE_SERVICE: Init ... !!!

[C7x_1 ] 17.927446 s: REMOTE_SERVICE: Init ... Done !!!

[C7x_1 ] 17.927468 s: VX_ZONE_INIT:Enabled

[C7x_1 ] 17.927480 s: VX_ZONE_ERROR:Enabled

[C7x_1 ] 17.927490 s: VX_ZONE_WARNING:Enabled

[C7x_1 ] 17.927652 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1

[C7x_1 ] 17.927718 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_2

[C7x_1 ] 17.927785 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_3

[C7x_1 ] 17.927906 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_4

[C7x_1 ] 17.927977 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_5

[C7x_1 ] 17.928049 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_6

[C7x_1 ] 17.928154 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_7

[C7x_1 ] 17.928221 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:59] Added target DSP_C7-1_PRI_8

[C7x_1 ] 17.928243 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

[C7x_1 ] 17.928256 s: APP: OpenVX Target kernel init ... !!!

[C7x_1 ] 17.928426 s: APP: OpenVX Target kernel init ... Done !!!

[C7x_1 ] 17.928441 s: APP: Init ... Done !!!

[C7x_1 ] 17.928451 s: APP: Run ... !!!

[C7x_1 ] 17.928460 s: IPC: Starting echo test ...

[C7x_1 ] 17.928627 s: APP: Run ... Done !!!

[C7x_1 ] 17.936458 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[x] C7X_1[s]

[C7x_1 ] 17.936918 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[P] C7X_1[s]

[C7x_1 ] 17.951162 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[s]

[C7x_1 ] 18.698431 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[s]

root@j7-evm:/opt/vision_apps# ./run_app_tidl.sh

APP: Init ... !!!

MEM: Init ... !!!

MEM: Initialized DMA HEAP (fd=4) !!!

MEM: Init ... Done !!!

IPC: Init ... !!!

IPC: Init ... Done !!!

REMOTE_SERVICE: Init ... !!!

REMOTE_SERVICE: Init ... Done !!!

630.260356 s: GTC Frequency = 200 MHz

APP: Init ... Done !!!

630.273850 s: VX_ZONE_INIT:Enabled

630.273890 s: VX_ZONE_ERROR:Enabled

630.273895 s: VX_ZONE_WARNING:Enabled

630.286275 s: VX_ZONE_INIT:[tivxInitLocal:130] Initialization Done !!!

630.286514 s: VX_ZONE_INIT:[tivxHostInitLocal:86] Initialization Done for HOST !!!

network file: /opt/vision_apps/test_data/tivx/tidl_models/tidl_net_mobilenet_v1.bin

config file: /opt/vision_apps/test_data/tivx/tidl_models/tidl_io_mobilenet_v1_1.bin

Iteration 0 of 1000000 ...

=================================

Demo : TIDL Object Classification

=================================

p: Print performance statistics

x: Exit

Enter Choice: p

Summary of CPU load,

====================

CPU: mpu1_0: TOTAL LOAD = 6.35 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu2_0: TOTAL LOAD = 3. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu2_1: TOTAL LOAD = 3. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c6x_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c6x_2: TOTAL LOAD = 0. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

HWA performance statistics,

===========================

DDR performance statistics,

===========================

DDR: READ BW: AVG = 392 MB/s, PEAK = 6630 MB/s

DDR: WRITE BW: AVG = 34 MB/s, PEAK = 2808 MB/s

DDR: TOTAL BW: AVG = 426 MB/s, PEAK = 9438 MB/s

Detailed CPU performance/memory statistics,

===========================================

CPU: mcu2_0: TASK: IPC_RX: 0. 0 %

CPU: mcu2_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CPU_0: 0. 0 %

CPU: mcu2_0: TASK: TIVX_NF: 0. 0 %

CPU: mcu2_0: TASK: TIVX_LDC1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_MSC1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_MSC2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_VISS1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP1: 0. 3 %

CPU: mcu2_0: TASK: TIVX_DISP2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT3: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT4: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT5: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT6: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT7: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT8: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP_M: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP_M: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP_M: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP_M: 0. 0 %

CPU: mcu2_0: HEAP: DDR_SHARED_MEM: size = 16777216 B, free = 4230912 B ( 25 % unused)

CPU: mcu2_0: HEAP: L3_MEM: size = 262144 B, free = 261888 B ( 99 % unused)

CPU: mcu2_1: TASK: IPC_RX: 0. 0 %

CPU: mcu2_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_1: TASK: TIVX_SDE: 0. 0 %

CPU: mcu2_1: TASK: TIVX_DOF: 0. 0 %

CPU: mcu2_1: TASK: TIVX_CPU_1: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: HEAP: DDR_SHARED_MEM: size = 16777216 B, free = 16773376 B ( 99 % unused)

CPU: mcu2_1: HEAP: L3_MEM: size = 262144 B, free = 262144 B (100 % unused)

CPU: c6x_1: TASK: IPC_RX: 0. 0 %

CPU: c6x_1: TASK: REMOTE_SRV: 0. 0 %

CPU: c6x_1: TASK: LOAD_TEST: 0. 0 %

CPU: c6x_1: TASK: TIVX_CPU: 0. 0 %

CPU: c6x_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: c6x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_1: HEAP: DDR_SHARED_MEM: size = 16777216 B, free = 16773376 B ( 99 % unused)

CPU: c6x_1: HEAP: L2_MEM: size = 229376 B, free = 229376 B (100 % unused)

CPU: c6x_1: HEAP: DDR_SCRATCH_MEM: size = 50331648 B, free = 50331648 B ( 14 % unused)

CPU: c6x_2: TASK: IPC_RX: 0. 0 %

CPU: c6x_2: TASK: REMOTE_SRV: 0. 0 %

CPU: c6x_2: TASK: LOAD_TEST: 0. 0 %

CPU: c6x_2: TASK: TIVX_CPU: 0. 0 %

CPU: c6x_2: TASK: IPC_TEST_RX: 0. 0 %

CPU: c6x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c6x_2: HEAP: DDR_SHARED_MEM: size = 16777216 B, free = 16773376 B ( 99 % unused)

CPU: c6x_2: HEAP: L2_MEM: size = 229376 B, free = 229376 B (100 % unused)

CPU: c6x_2: HEAP: DDR_SCRATCH_MEM: size = 50331648 B, free = 50331648 B ( 14 % unused)

CPU: c7x_1: TASK: IPC_RX: 0. 0 %

CPU: c7x_1: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_1: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0.22 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: TIVX_CPU_PR: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: HEAP: DDR_SHARED_MEM: size = 268435456 B, free = 243593728 B ( 10 % unused)

CPU: c7x_1: HEAP: L3_MEM: size = 8159232 B, free = 0 B ( 0 % unused)

CPU: c7x_1: HEAP: L2_MEM: size = 458752 B, free = 458752 B (100 % unused)

CPU: c7x_1: HEAP: L1_MEM: size = 16384 B, free = 0 B ( 0 % unused)

CPU: c7x_1: HEAP: DDR_SCRATCH_MEM: size = 402653184 B, free = 402646784 B ( 3 % unused)

GRAPH: app_tidl_graph (#nodes = 1, #executions = 2)

NODE: DSP_C7-1: TIDLNode: avg = 1969 usecs, min/max = 1350 / 2588 usecs, #executions = 2

GRAPH: Display (#nodes = 1, #executions = 2)

NODE: DISPLAY1: DisplayNode: avg = 125200 usecs, min/max = 119309 / 131091 usecs, #executions = 2

PERF: FILEIO: avg = 61711 usecs, min/max = 61203 / 62219 usecs, #executions = 2

PERF: DRAW: avg = 59367 usecs, min/max = 52065 / 66669 usecs, #executions = 2

PERF: TOTAL: avg = 252466 usecs, min/max = 249845 / 255088 usecs, #executions = 2

PERF: TOTAL: 3.96 FPS

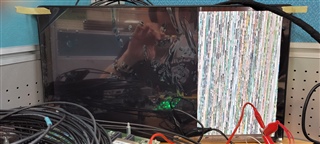

FPS is 3.96. It seems something there, BUT panel is BLACK.

Please help me debug this situation.

Thanks

Michael