hi expert:

On our cecu, two TDA4 PCIes are connected together by chip to chip. The PCIe controller is using pcie1. Set parameters, gen3, 2 lan. We found that when pcie starts enumeration, occasionally it can only enumerate to 1 lan. We tested the eye diagram of the cecu pcie and it looks very good. When only 1 lan can be enumerated, we dumped the registers related to pcie1 and serdes_16G1 and compared them with the normal enumerated registers, and found some differences. We cannot further analyze these register differences. Ask ti experts to help analyze the possible causes of the problem. Thanks!

The register dump file is attached.

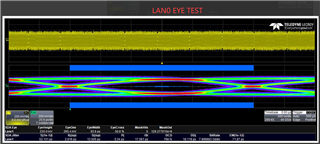

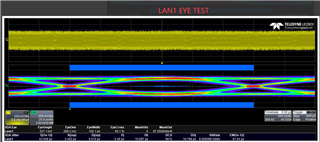

The eye diagram is as follows:

reg compare is as follows: