Hi, engineers of TI,

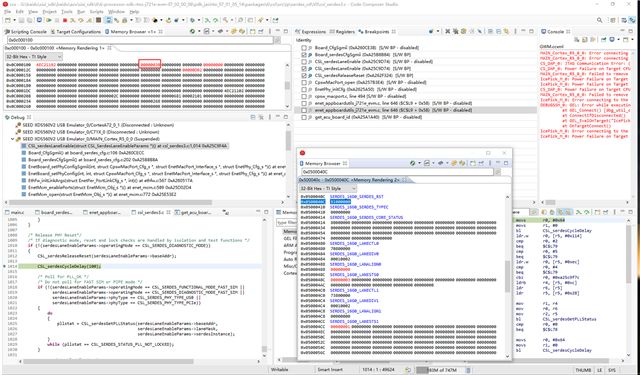

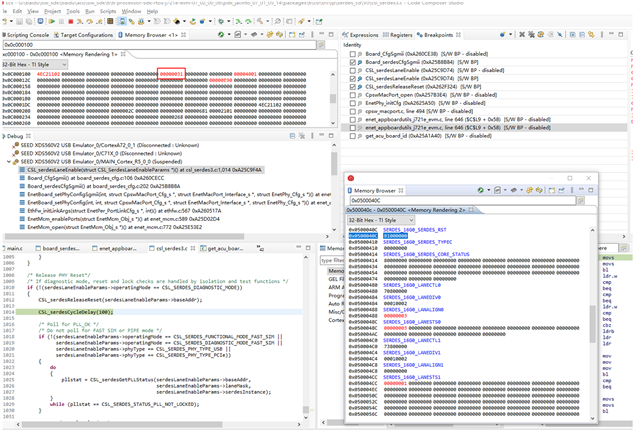

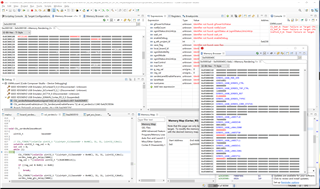

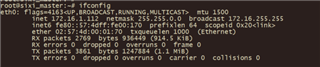

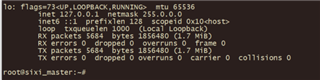

Some times , we got eth0 mount fail, then we checked mcu2_0 log, we can see program hangs down below:

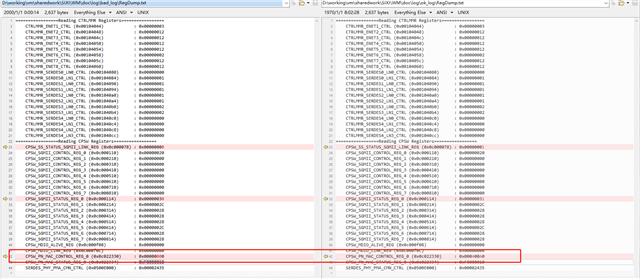

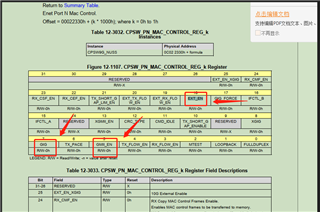

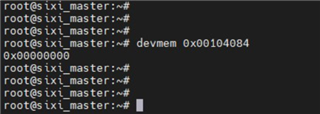

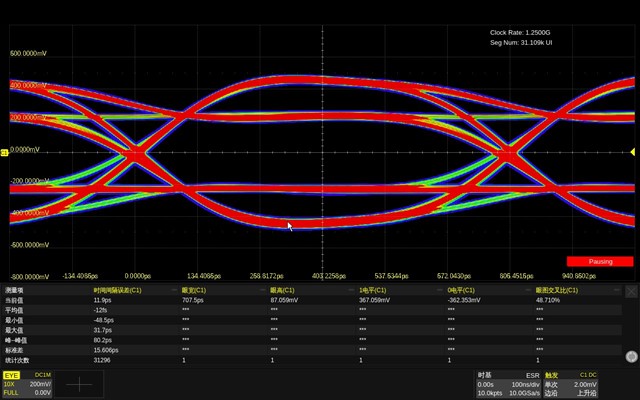

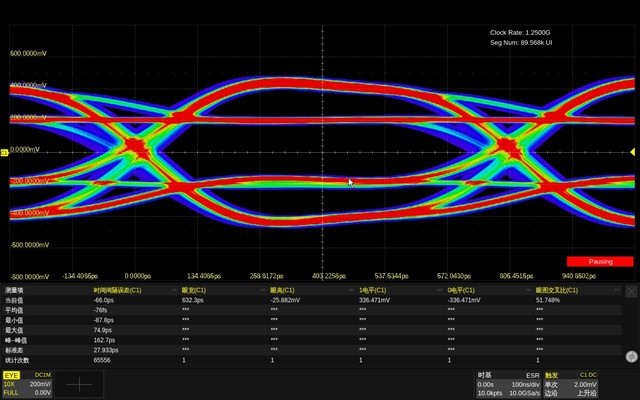

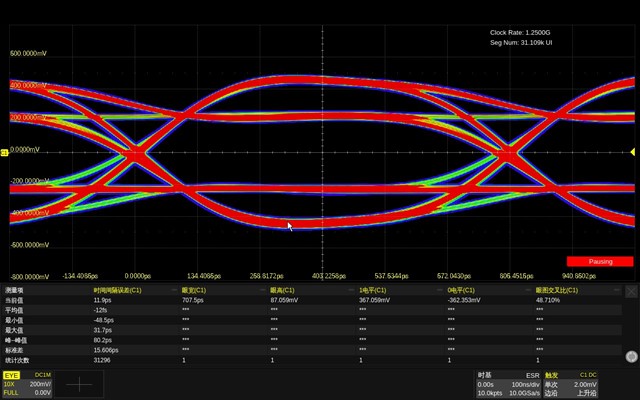

Then we checked the sgmii register status ,we got 0x00000030

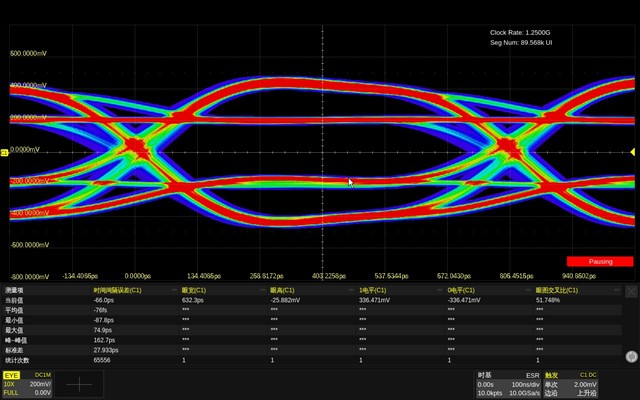

After that, we checked PHY link status, and it is link up!

TDA4 isn't update sgmii link status in the initialization phase, please help us to check how dose it happend.

Thanks a lot.

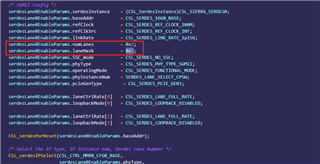

but we just get this

but we just get this  when the sgmii link status gose wrong.

when the sgmii link status gose wrong.