Part Number: AM3357

Hi Team,

Please confirm the following about the power supply of AM335x.

If VDDSHV (3.3 V) is about 800 mV @ 120 ms before rising, is it OK before RESET?

(no RTC functionality)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM3357

Hi Team,

Please confirm the following about the power supply of AM335x.

If VDDSHV (3.3 V) is about 800 mV @ 120 ms before rising, is it OK before RESET?

(no RTC functionality)

Hi Shinnosuke,

Thanks for the query,

Could you please share the waveform that is captured till the POR reset release.

Also please share what power solution is used.

Regards,

Kalyan.

Hi,

Thank you for your reply.

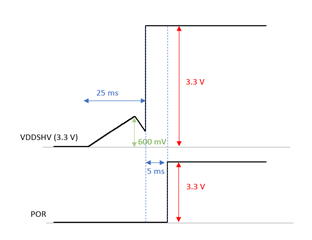

The circuit has been changed and the waveform is as follows.

The power solution is Power-Supply Sequencing With RTC Feature Disabled.

Best regards,

Kaneko

Hi Shinnosuke,

Please provide the waveform captured with 1.8V, 3.3V and POR.

What power solution that you are using. Is it PMIC or discrete?

How 3.3V is enabling? Is there any leakage path in 3.3V?

Thanks,

Kalyan.

Hi,

Thank you for your reply.

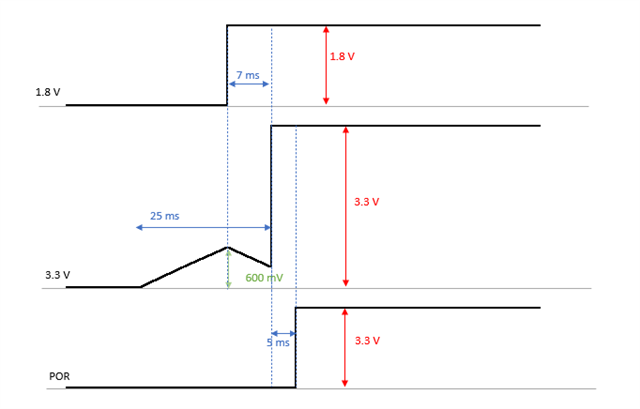

The waveforms for 1.8 V, 3.3 V, and POR are as follows.

The power solution is discrete.

The FPGA is connected to the AM3357.

The FPGA power supply (+ 3.3 V _ FPGA) is supplied before the AM3357 power supply (+ 3.3 V _ AM 3357).

During the FPGA configuration, the signal line is pulled up, so we think it is leaking.

Hi Shinnosuke,

Since the 3.3V leakage is within the absolute maximum ratings of VDDSHV and before POR release.

It should be fine.

Thanks,

Kalyan.