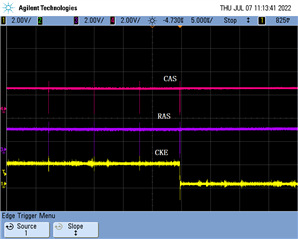

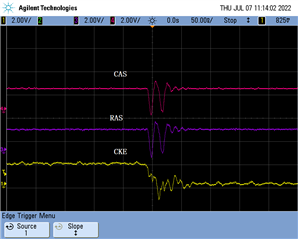

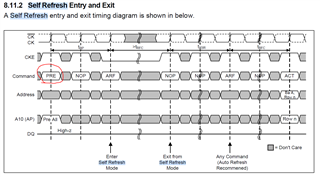

From mDDR spec, there should be a Precharge command before self-refresh command, We captured signal, did not find Precharge command, only enter self-refresh command.

DDR2 spec doesn't need precharge command before entering self-refresh command. The DDR control behave same for DDR2 and mDDR.

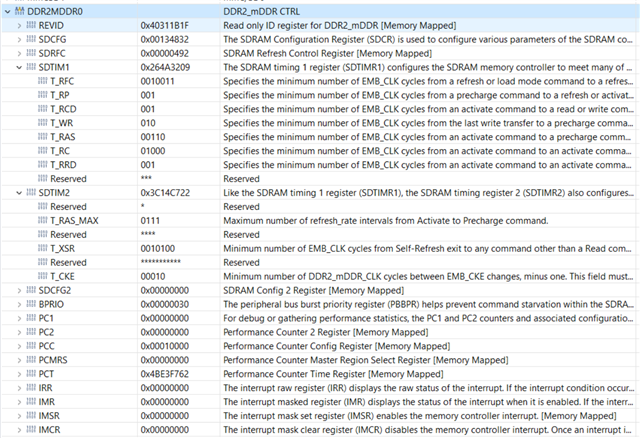

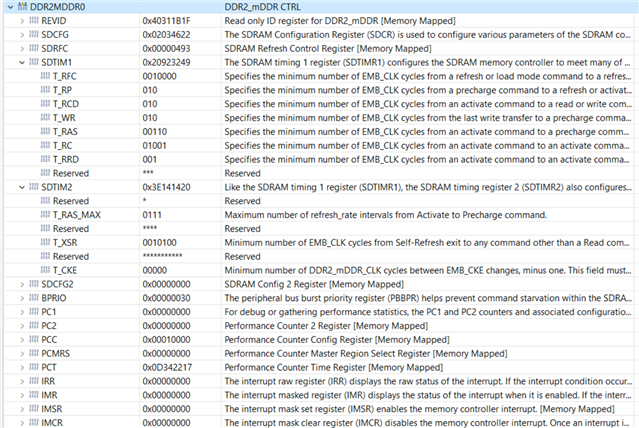

Enter self refresh as below form gel:

hotmenu enter_ddr_selfrefresh()

{

//*(unsigned int *)0xc0000000 =0xaaaa5555;

EMIFDDR_SDRCR &= ~(1<<23);

EMIFDDR_SDRCR |=1<<31;

}

As with Winbond mDDR has problem on exit self refresh, and it need precharge command as below

Is there any special command to send out precharge command with enter self refresh command?