Other Parts Discussed in Thread: TDA4VM, DRA829

Hi All,

We are facing a issue in custom designed TDA4VM hardware when we running following applications

- run_app_srv.sh

- run_app_tidl_od.sh - with disabling display in cfg file

- stress-ng --cpu 2

with the above tests we are seeing two different behaviors in our custom TDA4VM boards.

Issue1:

When we run the above tests in TDA4VM generic chip( Non- HS version) the display is broken and boards hangs after some time ( ~1.5hours)

Issue 2:

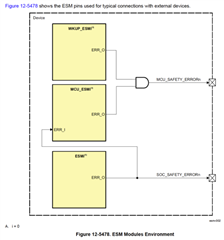

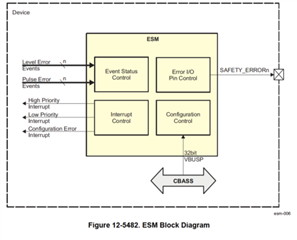

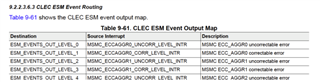

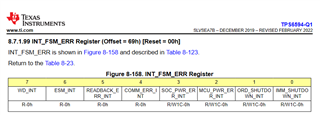

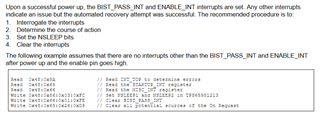

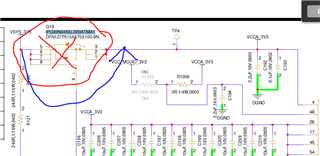

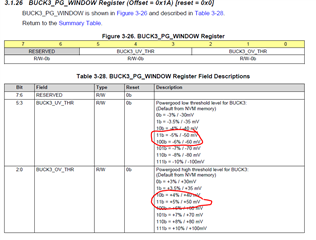

When we run the above tests in TDA4VM HS version chip the board reboots after 20 Seconds after running above mentioned tests. In this scenario we sees SOC_SAFETY_ERRORn signal and MCU_SAFETY_ERRORn signals get asserted and shall be reported to PMIC which is causing board reboot.

Kindly request to provide us the pointers to debug this.

Regards,

Chaitanya