Hi,

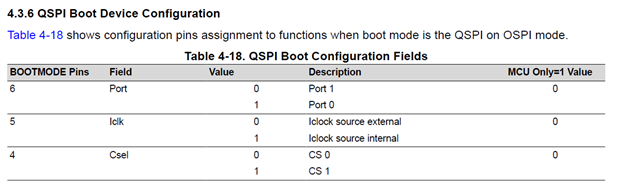

I wish to boot the DRA829J's MCU from QSPI (Normal bootmode). The OSPI port0 will be connected to a QSPI device using 6pins (DQ0-3, OCLK and SS) What does the lclk pin config do here?. I'm thinking I need to set it to 1 (internal) so the OCLK is sourced from the OSPI module internally to drive the QSPI?.

thanks