Hi,

We need to create uninterrupted transmission over SPI channel.

We enabled TX FIFO and make sure that we fill FIFO and do not get "FIFO full" condition.

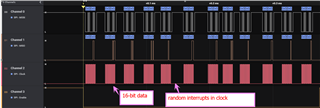

Logic analyzer shows random gaps in clock between 16-bit frames (SPI is configured as 16-bit).

Does TI implementation guaranty that gapless SPI transmission under condition that TX FIFO does not get empty?

Thanks

Rasty