Other Parts Discussed in Thread: DRA821

Hello,

We are using DRA821 UDMA to load a large mount of code in NorFlash to RAM during the initialization, and we found it took much more time than we expected.

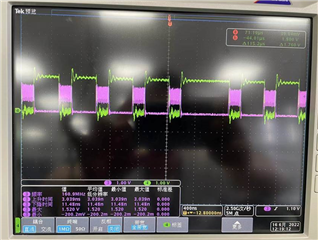

Following is the signals of CS and data line captured by oscilloscope. The green signal is CS, and the purple one is data line. We consult the NorFlash provider(IFX, s28hs512t) that there shall be a minimum interval between every read command called dummy cycles, and as shown in below figure, there are two many dummy cycles which result in low usage of data transformation. In other words, we want to increase the data length of every read command, which can significantly reduce the "idle" time between each read command.

However, we can't find the way to configure it. For UDMA, we can only configure UDMA read total size which the size of whole software code, and the UDMA utilizes OSPI DAC mode to direct access NorFlash.

Do you have any idea how to solve this problem?

Thank you very much!