Part Number: TDA4VM

Hi,

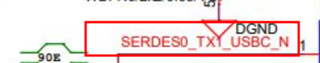

We would like to use the USB 3.0 TYPE A (host, super speed). As we know that the SDK(8.0.4) configures the SERDES to support EDP + PCIe.

Could you provide a sample Linux device tree configure to support USB + EDP?

USB -> LANE1

EDP->LANE 2 and LANE3

Thanks,

Ethan