Hi ,TI expert,

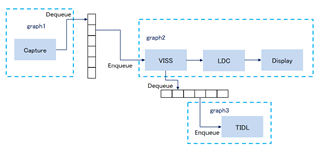

I have the 3 graph ,the design is as below. my os is qnx+rtos ,sdk version is 8.0 ,and 6 channel camera,but only connect with 1 camera.

-

- 1. running the 3 graphs demo, get a tearing or split image with curve line

-

- 2. remove the ldc node in graph2, curve line become to straight line

- 3. tidl is running normal,but load local file(vpac MSC not using) ,the display node still show image with straight line.

- 4. create a seperate process for graph3(tidl),the phenomena still exist.

here's my question,

i would like to kown how caused the image data corruption?

1. are the three graph3 links correct?

graph1(only capture node) dequeue the raw data,and enqueue to the second graph(viss -> ldc->display) to show the camera images.graph2 dequeue the rgb image data from ldc ,enqueue to tidl which there are multi cnn model runing

2. graph2 using vpac(viss ldc) and graph3 using vpac(msc) together is ok? in other words ,could the vpac be used by multi graphs?

3. as above step2 ,remove the ldc node ,the "curve" become "straight",Would i specify that the dirty data is imported before the LDC node ?

4. in the openvc /tiovx framework ,Whether the buffer shared by two nodes has a protection mechanism when dequeue or enqueue operation?

i think if the previous node is using a buffer , the next node will not get a pointer to the same buffer, and buffer depth set is 4

The problem has been investigated for a long time, but the problem cannot be located.

In the course of my experiments, I found that once the TIDL module is running, the image must be corrupted .

when tidl graph running, the a72 and c71 are not running at full capacity, but the sensor fps (capture node performance) is very unstable. I don't know if that's going to cause the problem.

any advice is very appeciate,thanks