Hi team,

Here's an issue from the customer may need your help:

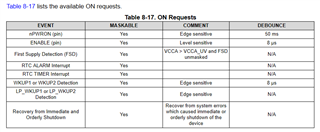

In the 0C reference design of the PMIC, GPIO4 of PTPS65941213RWERQ1 is configured to WAKE signal. Is the state of this signal must be a change in the high or low level, or is it ok to be high all the time?

For example, GPIO4 is high when PTPS65941213RWERQ1 is working properly, and then GPIO4 is always high during PTPS65941213RWERQ1 going from active to LP_standby. Then the LP_standby state is also high, will the PMIC go back to active?

Could you help check this case? Thanks.

Best Regards,

Cherry