Part Number: TDA4VM

Other Parts Discussed in Thread: TDA4VL

Hi Brijesh,

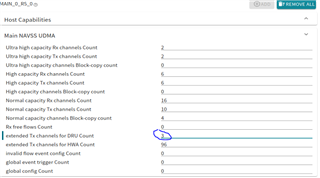

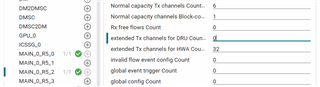

When the abnormal occurs, I find that the errorFrameCount is incremented in function CsirxDrv_udmaCQEventCb.

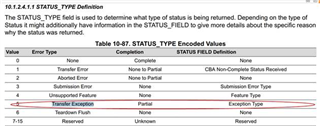

The condition is judged by errorFrameCount, and the cause of the exception is Transfer Exception. The details are as follows:

Analysis of Transfer Exception shows that the reason is EOP on incoming data stream was encountered prematurely (short packet), the details are as follows:

Do you have any good comments?

I'll add more details later.

BR,

Lei