Dear experts,

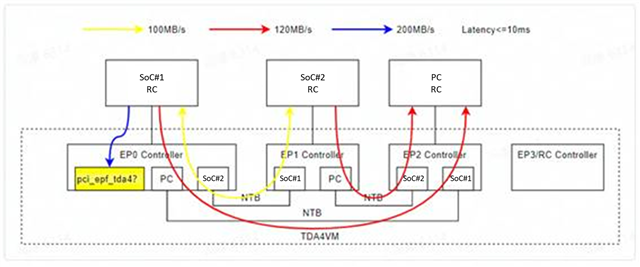

Referring to the SDK example, our customer wants to use below PCIe structure. TDA4VM is used as PCIe Backplane mode. Compared to the SDK example, the main difference is that there is a more function (they call pci_epf_tda4) used for receive data from SoC#1 in EP0 controller. SoC#1 and SoC#2 is other company's SoC.

Data path including:

- SoC#1 => TDA4: 200MB/s

- SoC#1 <=> SoC#2: 100MB/s

- SoC#1 => PC: 120MB/s

- SoC#2 => PC: 120MB/s

Their question is,

- Does TDA4VM PCIe support this structure? Can TDA4VM support these 3 NTB configuration?

- Can EP0 controller add this function (pci_epf_TDA4)? Do we have sample code for this function?

- Can SoC#1 send data to pcie_epf_tda4, PC and SoC#2 at the same time?

- If pci_epf_tda4 can be supported, what is the implementation form? Socket or lib? Can be virtual internet card?

- Can TDA4VM meet the bandwidth and latency (<=10ms) requirement?

- To realize this function, does SoC#1 need 2 virtual internet card (one connect to SoC#2, another connect to PC)?

Thanks

Best Regards