Hi team,

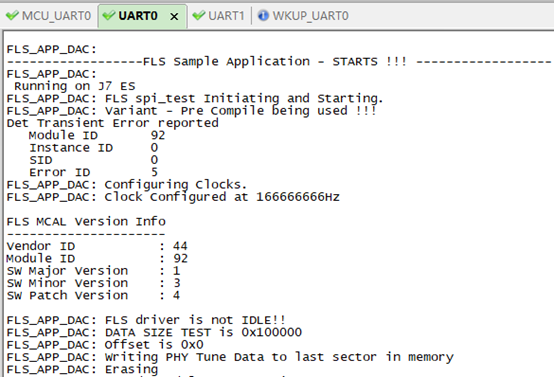

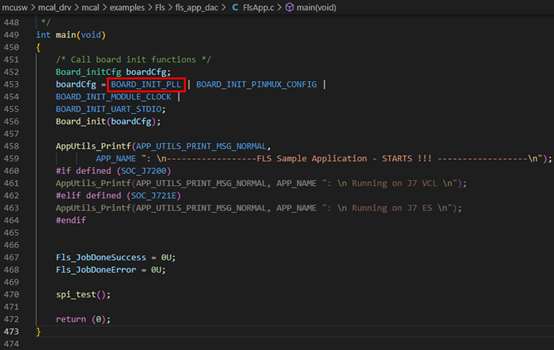

Debugging under ti-processor-sdk-rtos-j721e-evm-08_02_00_05, the customer found that the board initialization function Board_init() cannot be used to configure the PLL. The fls_app_dac demo routine compiled with the original code of the unchanged PSDK under mcusw, the following is the result of loading and running it in the CCS environment. Among them, DMSC loads and runs the sysfw file ti-fs-firmware-j721e-gp.bin. mcu1_0 loads and runs sciserver_testapp_freertos_mcu1_0_release.xer5f. mcu2_1 loads and runs fls_app_dac_mcu2_1_release.xer5f.

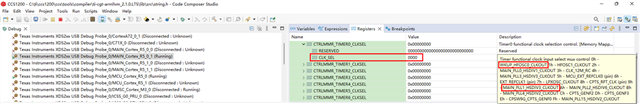

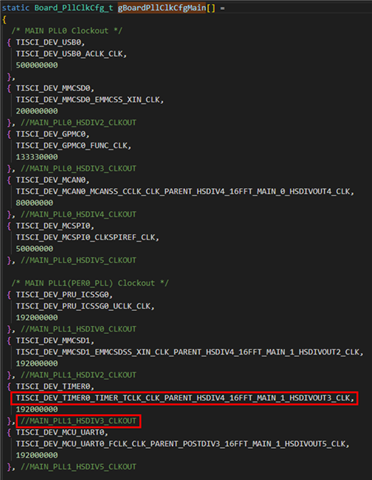

The clock source configuration of TIMER0 is configured in board_pll.c. The running program did not report any errors when executing Board_init(). But as a result, the clock source selection register CTRLMMR_TIMER0_CLKSEL of TIMER0 has not changed (the correct configuration register value should be 9). The initialization configuration of BOARD_INIT_PLL by Board_init() does not take effect.

Would you help to check what's wrong?

Thanks.

Annie