Other Parts Discussed in Thread: SYSCONFIG,

Hello TI,

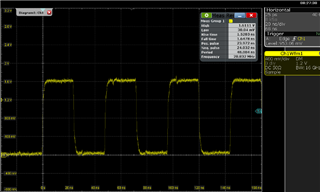

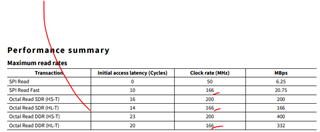

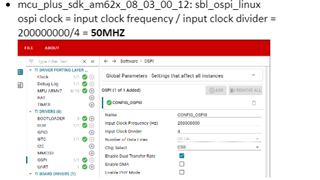

Boot ROM with 50 MHz for 1-1-1 mode, and 25 MHz for 8-8-8 mode with fast read command.

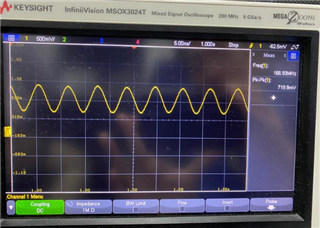

With SPL bootloader, I check the clock speed of OSPI is still ~ 25 MHz on Linux. I want to speed up to 166 MHz. How can I do?

Thanks,

Brian