HI TI,

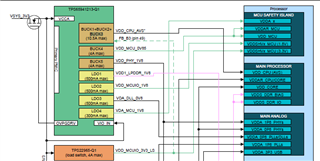

My device:TDV4VM

OS:A core:QNX ,MCU_R5:AUTOSAR,others cores:TI RTOS

-

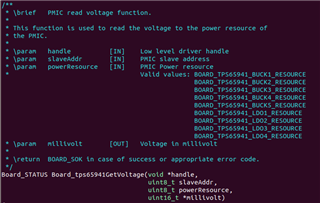

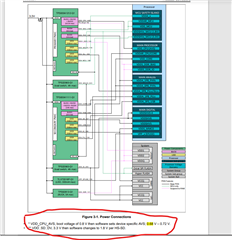

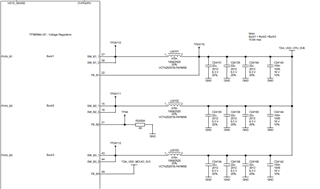

1.We intend to use AVS to dynamically adjust the voltage.However, we only see the AVS voltage set, but we don't see the relevant function to perform the voltage adjustment process, which makes me feel that the voltage is always fixed.

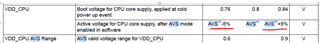

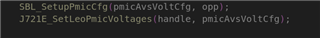

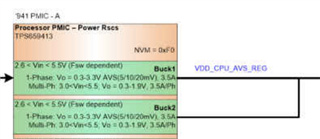

- 2.J721E_SetupLeoPmicAvs(SBL_OPP_NOM); This function sets the AVS voltage. I also know that there are 4 OPPS, but who decides when to jump from one OPP to another.Is it the software decision or the hardware decision? If it is the software decision, do we need to define the relevant functions ourselves

- 3.How should I configure the OPP, the DATASHEET only gives the value of the voltage in the read and write OPPS, but there is no place to configure the connection between voltage and frequency

![]()

Best regard,

guangjie.lin