- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi ,

could you please share the info about LVDS and how to configure in DTS and as well as in kernel .

Thanks,

Naresh

Hi Krunal ,

Thanks for patch dual display patch.

actually our setup is single channel display ,accordingly we configured the LVDS in device tree .

we just observed light vertical lines on the display .

please let us know what are the changes required to make get the LVDS display

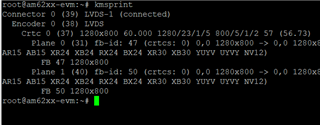

we got the kmstest and modetest response as below :

oot@am62xx-evm:/sys/class/drm/card0-LVDS-1# kmsprint

[ 2965.061449] line=88 fun=panel_lvds_get_modes

Connector 0 (39) LVDS-1 (connected)

Encoder 0 (38) LVDS

Crtc 0 (37) 1280x800 68.200 1280/64/1/5 800/40/1/2 60 (59.93)

Plane 0 (31) fb-id: 47 (crtcs: 0) 0,0 1280x800 -> 0,0 1280x800 (AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YU)

FB 47 1280x800

Plane 1 (40) fb-id: 51 (crtcs: 0) 0,0 1280x800 -> 0,0 1280x800 (AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YU)

FB 51 1280x800

root@am62xx-evm:/sys/class/drm/card0-LVDS-1# kmstest

[ 2969.758164] line=88 fun=panel_lvds_get_modes

Could not get DRM master permission. Card already in use?

root@am62xx-evm:/sys/class/drm/card0-LVDS-1# modetest -M tidss

[ 3564.430778] line=88 fun=panel_lvds_get_modes

Encoders:

id crtc type possible crtcs possible clones

38 37 LVDS 0x00000001 0x00000001

Connectors:

id encoder status name size (mm) modes encoders

39 38 connected LVDS-1 153x117 1 38

modes:

index name refresh (Hz) hdisp hss hse htot vdisp vss vse vtot)

#0 1280x800 59.93 1280 1344 1345 1350 800 840 841 843 68200 flags: ; type: preferred, driver

props:

1 EDID:

flags: immutable blob

blobs:

value:

2 DPMS:

flags: enum

enums: On=0 Standby=1 Suspend=2 Off=3

value: 0

5 link-status:

flags: enum

enums: Good=0 Bad=1

value: 0

6 non-desktop:

flags: immutable range

values: 0 1

value: 0

4 TILE:

flags: immutable blob

blobs:

value:

20 CRTC_ID:

flags: object

value: 37

CRTCs:

id fb pos size

37 47 (0,0) (1280x800)

#0 1280x800 59.93 1280 1344 1345 1350 800 840 841 843 68200 flags: ; type: preferred, driver

props:

22 ACTIVE:

flags: range

values: 0 1

value: 1

23 MODE_ID:

flags: blob

blobs:

value:

680a0100000540054105460500002003

480349034b0300003c00000000000000

48000000313238307838303000000000

00000000000000000000000000000000

00000000

19 OUT_FENCE_PTR:

flags: range

values: 0 18446744073709551615

value: 0

24 VRR_ENABLED:

flags: range

values: 0 1

value: 0

27 CTM:

flags: blob

blobs:

value:

28 GAMMA_LUT:

flags: blob

blobs:

value:

29 GAMMA_LUT_SIZE:

flags: immutable range

values: 0 4294967295

value: 256

Planes:

id crtc fb CRTC x,y x,y gamma size possible crtcs

31 37 47 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 1

17 FB_ID:

flags: object

value: 47

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 37

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 1280

16 CRTC_H:

flags: range

values: 0 2147483647

value: 800

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 83886080

12 SRC_H:

flags: range

values: 0 4294967295

value: 52428800

32 zpos:

flags: range

values: 0 1

value: 0

33 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

34 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

35 alpha:

flags: range

values: 0 65535

value: 65535

36 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

40 37 51 0,0 0,0 0 0x00000001

formats: AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12

props:

8 type:

flags: immutable enum

enums: Overlay=0 Primary=1 Cursor=2

value: 0

17 FB_ID:

flags: object

value: 51

18 IN_FENCE_FD:

flags: signed range

values: -1 2147483647

value: -1

20 CRTC_ID:

flags: object

value: 37

13 CRTC_X:

flags: signed range

values: -2147483648 2147483647

value: 0

14 CRTC_Y:

flags: signed range

values: -2147483648 2147483647

value: 0

15 CRTC_W:

flags: range

values: 0 2147483647

value: 1280

16 CRTC_H:

flags: range

values: 0 2147483647

value: 800

9 SRC_X:

flags: range

values: 0 4294967295

value: 0

10 SRC_Y:

flags: range

values: 0 4294967295

value: 0

11 SRC_W:

flags: range

values: 0 4294967295

value: 83886080

12 SRC_H:

flags: range

values: 0 4294967295

value: 52428800

41 zpos:

flags: range

values: 0 1

value: 1

42 COLOR_ENCODING:

flags: enum

enums: ITU-R BT.601 YCbCr=0 ITU-R BT.709 YCbCr=1

value: 0

43 COLOR_RANGE:

flags: enum

enums: YCbCr limited range=0 YCbCr full range=1

value: 0

44 alpha:

flags: range

values: 0 65535

value: 65535

45 pixel blend mode:

flags: enum

enums: Pre-multiplied=0 Coverage=1

value: 0

Frame buffers:

id size pitch

root@am62xx-evm:/sys/class/drm/card0-LVDS-1#

thanks ,

Naresh

hi Krunal

We are trying to bring up LVDS on AM625- custom platform,

The patch is for Dual channel LVDS , but we are using single channel (using port@0 only) for our LVDS setup

The output of kmstest as below , (display shows some lines)

root@am62xx-evm:~# killall -9 weston ; kmsprint ; kmstest -c LVDS-1 -r 1280x800

killall: weston: no process killedton ; kmsprint ; kmstest -c LVDS-1 -r 1280x800

Connector 0 (39) LVDS-1 (connected)

Encoder 0 (38) LVDS

Crtc 0 (37) 1280x800 68.200 1280/64/2/5 800/40/1/2 60 (59.88)

Plane 0 (31) fb-id: 46 (crtcs: 0) 0,0 1280x800 -> 0,0 1280x800 (AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 AR15 AB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12)

FB 46 1280x800

Connector 0/@39: LVDS-1

Crtc 0/@37: 1280x800 68.200 1280/64/2/5/? 800/40/1/2/? 60 (59.88) 0 0x48

Plane 0/@31: 0,0-1280x800

Fb 47 1280x800-XR24

press enter to exit

below is LCD output :

-nagendra

Okay, have you gone through the patches to understand how we enabled dual link? Here is an example of what a customer did to use our patches and enable single link panel: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1128751/am625-oldi-driver-or-dts-example/4199484#4199484

Regards,

Krunal

Hi Krunal ,

we followed the same which one of the customer did for single channel display in that thread , even though our disaplay not getting .[ which appears as we posted in prevoius thread ].

may i know what's these settings for ->

uenvcmd=if run check_psdk_setup; then echo "Already setup."; else run do_psdk_setup; mw.b ${loadaddr} 0 1; fatwrite mmc 1:1 ${loadaddr} .psdk_setup 1; reset; fi; mw.l 0x00109008 0x68EF3490; mw.l 0x0010900C 0xD172BC5A; mw.l 0x00108700 0x00000000;

Thanks,

Naresh

The Uboot change enables the OLDITX IP because by default they are powered off. Please share the LCD dts file.

Regards,

Krunal

Hi Naresh,

The DTS file looks okay and have you tried to probe the PCLK/data lines to ensure everything is meeting your spec? Also, please check with your LCD vendor to ensure timing parameters are correct.

Regards,

Krunal

Hi Krunal

we could get the LVDS clock-0 and data lines toggling , the clock is matching with our configured value (signals, OLDI0_A0/A2/A3/A4 and OLDI0_CLK0)

-nagendra

Hello nagendra,

My recommendation would be to check with the timing parameters of your LCD. On my setup, I got a single channel LVDS to work and here are my changes:

diff --git a/arch/arm64/boot/dts/ti/k3-am625-sk-oldi-panel.dts b/arch/arm64/boot/dts/ti/k3-am625-sk-oldi-panel.dts

index 600955e89a06..d8d87c654eac 100644

--- a/arch/arm64/boot/dts/ti/k3-am625-sk-oldi-panel.dts

+++ b/arch/arm64/boot/dts/ti/k3-am625-sk-oldi-panel.dts

@@ -25,31 +25,24 @@

data-mapping = "vesa-24";

panel-timing {

- clock-frequency = <150280000>;

- hactive = <1920>;

- vactive = <1200>;

- hback-porch = <32>;

- hfront-porch = <52>;

- vback-porch = <24>;

- vfront-porch = <8>;

- hsync-len = <24>;

- vsync-len = <3>;

+ clock-frequency = <71100000>;

+ hactive = <1280>;

+ vactive = <800>;

+ hback-porch = <48>;

+ hfront-porch = <32>;

+ vback-porch = <2>;

+ vfront-porch = <5>;

+ hsync-len = <80>;

+ vsync-len = <16>;

de-active = <1>;

};

port@0 {

- dual-lvds-even-pixels;

lcd_in0: endpoint {

remote-endpoint = <&oldi_out0>;

};

};

- port@1 {

- dual-lvds-odd-pixels;

- lcd_in1: endpoint {

- remote-endpoint = <&oldi_out1>;

- };

- };

};

};

};

@@ -66,18 +59,8 @@

AM62X_IOPAD(0x026c, PIN_OUTPUT, 0) /* (AA8) OLDI0_A2P */

AM62X_IOPAD(0x0278, PIN_OUTPUT, 0) /* (AB6) OLDI0_A3N */

AM62X_IOPAD(0x0274, PIN_OUTPUT, 0) /* (AA7) OLDI0_A3P */

- AM62X_IOPAD(0x0280, PIN_OUTPUT, 0) /* (AC6) OLDI0_A4N */

- AM62X_IOPAD(0x027c, PIN_OUTPUT, 0) /* (AC5) OLDI0_A4P */

- AM62X_IOPAD(0x0288, PIN_OUTPUT, 0) /* (AE5) OLDI0_A5N */

- AM62X_IOPAD(0x0284, PIN_OUTPUT, 0) /* (AD6) OLDI0_A5P */

- AM62X_IOPAD(0x0290, PIN_OUTPUT, 0) /* (AE6) OLDI0_A6N */

- AM62X_IOPAD(0x028c, PIN_OUTPUT, 0) /* (AD7) OLDI0_A6P */

- AM62X_IOPAD(0x0298, PIN_OUTPUT, 0) /* (AD8) OLDI0_A7N */

- AM62X_IOPAD(0x0294, PIN_OUTPUT, 0) /* (AE7) OLDI0_A7P */

AM62X_IOPAD(0x02a0, PIN_OUTPUT, 0) /* (AD4) OLDI0_CLK0N */

AM62X_IOPAD(0x029c, PIN_OUTPUT, 0) /* (AE3) OLDI0_CLK0P */

- AM62X_IOPAD(0x02a8, PIN_OUTPUT, 0) /* (AE4) OLDI0_CLK1N */

- AM62X_IOPAD(0x02a4, PIN_OUTPUT, 0) /* (AD5) OLDI0_CLK1P */

>;

};

};

@@ -98,24 +81,4 @@

remote-endpoint = <&lcd_in0>;

};

};

-

- /* VP1: LVDS Output (OLDI TX 1) */

- port@2 {

- reg = <2>;

- oldi_out1: endpoint {

- remote-endpoint = <&lcd_in1>;

- };

- };

-};

-

-&main_i2c1 {

- #address-cells = <1>;

- #size-cells = <0>;

-

- touchscreen@41 {

- compatible = "ilitek,ili251x";

- reg = <0x41>;

- interrupt-parent = <&exp1>;

- interrupts = <15 IRQ_TYPE_EDGE_FALLING>;

- };

};

The timing varies based on the manufacture so verify your datasheet.

Regards,

Krunal

hello Krunal

yes we verified our timings are correct, all LVDS signals are toggling as expected (A0-A3) , clk0 is observed as expected

still, we could not get our display working, the output on lvds display is as before

since drm/card0-lvds node is present and all signals are toggling , can we rule out software dependency ?

-Nagendra

Yes, I don't think it's a software dependency. Also, if you run kmstest, does your LVDS node enumerate? Also, it should print the timing values that corresponds to the DTS entry. If the answer is yes, we know the driver is configured and DSS IP is sending the correct signals to the panel.

Regards,

Krunal

Krunal

yes, the kmstest provides the timing details according to our DTB , also LVDS node info , and activity observed in all LVDS signals

any suggestion to check and confirm HW side ?

-nagendra

Are you observing the gradient issue on all the panels or just one? Also, you may have to probe clock and pixel data simultaneously and ensure all the data is latching on the appropriate falling edge or rising edge. Also, check with the panel vendor on possible issues that could contribute to gradients. Also, please ensure that data-mapping "vesa-24" matches your panel requirement.

Regards,

Krunal