hi experts,

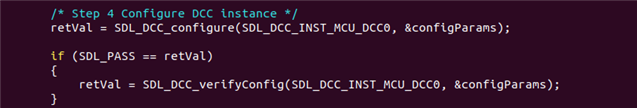

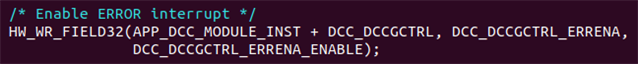

I'm trying to understand the default code of DCC inside the SDL package, the folder as : SDL_1.0/SDL_RLS_01.00.00/sdl/examples/dcc/UC8.

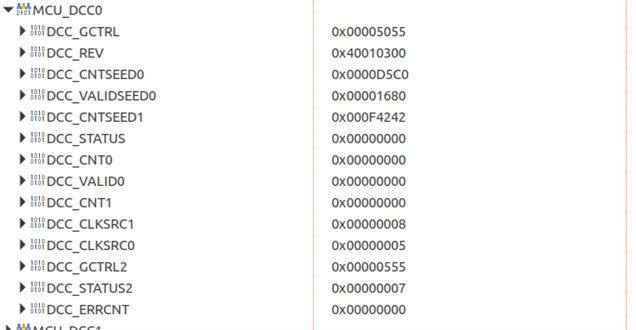

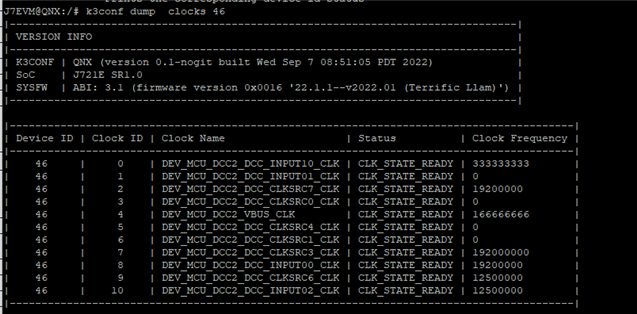

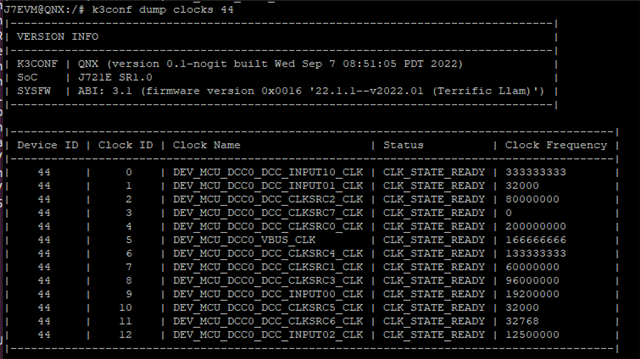

the Source clock is RC OSC and Test clock is HFOSC0, I also can understand the HFOSC0 is 19200(19.2MHZ), but what's the RC OSC clock? I see it's 333334 in the code, But I only can see it’s 12.5MHZ in the TRM, could you please guide us what's this and is it related with the HW?

and also, why we choose this clock 333334 as input, is it determined by HW connection?

thanks in advance.

Br,

Neo