Hi,

I am using a C6713 with high-precision ADS8556 ADC's.

Here is my situation to receive data from ADS8556 using McASP.

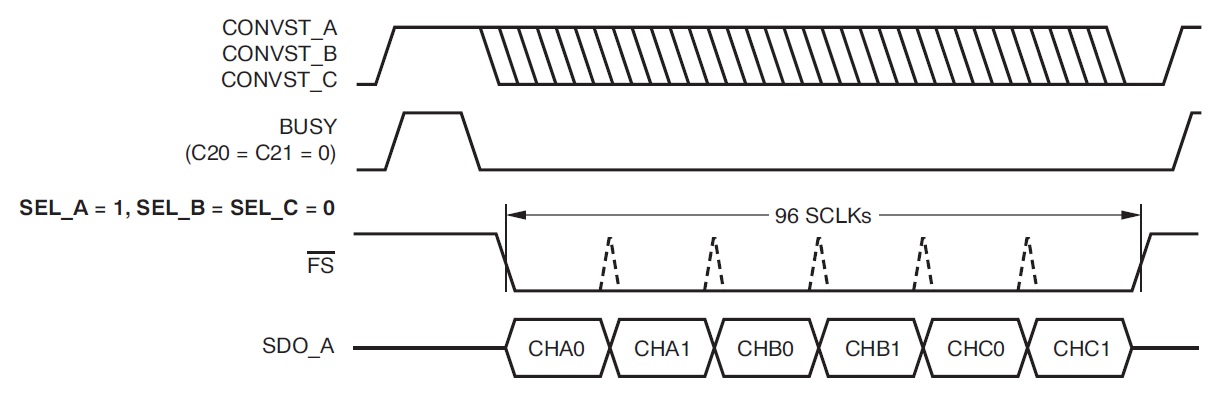

I have 6 channels of data coming from ADS8556 coming into the McASP1 serializer 5 (say)

in TDM Mode and another 6 channels of data coming from another ADS8556 into serializer 6

also in TDM mode. How do I set up the McASP for the operation especially to get a frame-sync that is low for 96 clocks?

Please see the following timing diagram that the ADC expects especially the frame-sync.

Also CONVST_A/CONVST_B/CONVST_C in the design is tied to GPIO5/EXT_INT5.

How can I generate the CONVST_A pulse as can be seen if I were to use DSP/BIOS?

Thanks,

Aditi.