Hi Experts,

I am trying to figure out how to connect some of the clocks to set up the J721S2 Dual Clock Comparators.

The J721E chip has 13 DCCs while the J721S2 has only 10.

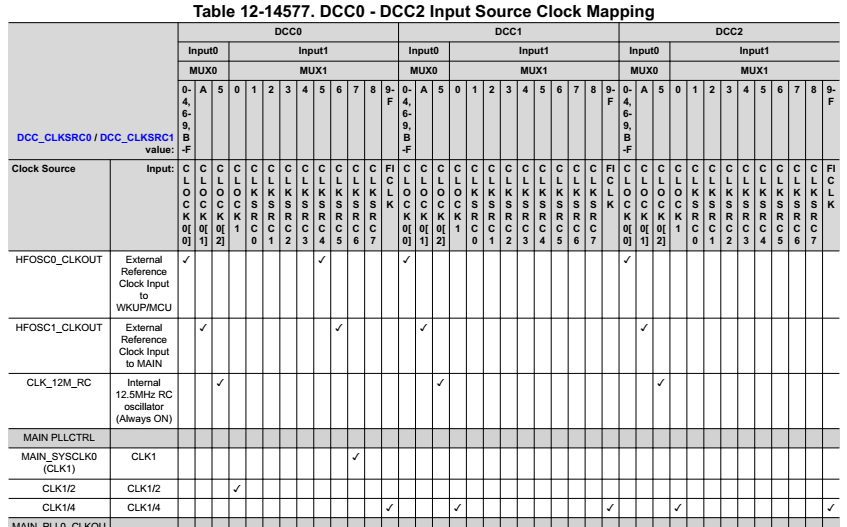

Looking at table 12-14577 in the J721E TRM (was unable to find in J721S2 TRM) I was able to get one instance to work correctly in single shot mode. MAIN DCC1, MAIN_PLL1_HSDIV6_CLKOUT (19.2MHz) and CLK_12M_RC (12.5MHz).

I have tried various combinations in other DCCs and the DCC has an error status before starting to count down the counters.

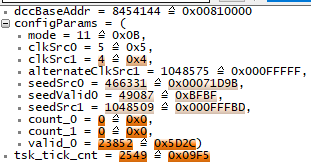

The values seem correct in the configuration struct but doesn’t work as expected.

Do the DCCs for the J721S2 line up with DCC 0-9 in table 12-14577 in the TRM or is it a different table matrix?