Hi, expers:

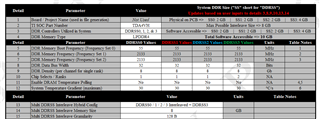

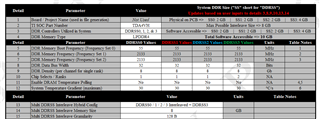

Does tda4vh supported 2GB + 2GB + 2GB + 4GB ddr config? Out ddr config as follow :

The the system got stuck on ddr4 probe (uboot-r5-spl).

Out tda4vh board can boot success on 2GB + 2GB + 2GB + 2GB ddr config.

Thanks

quanli

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi, expers:

Does tda4vh supported 2GB + 2GB + 2GB + 4GB ddr config? Out ddr config as follow :

The the system got stuck on ddr4 probe (uboot-r5-spl).

Out tda4vh board can boot success on 2GB + 2GB + 2GB + 2GB ddr config.

Thanks

quanli

Hi,

The hardware does support 2GB on DDRSS0, 1, 2 and 4GB on DDRSS3.

The issue here is likely related to a single define of "DDRSS_PLL_FHS_CNT" that is getting used by all 4x DDRSS, when in reality they should be different.

I am assuming that you currently have DDRSS_PLL_FHS_CNT = 6 in your DTSI file. Is that correct? If so, can you make the change below to the file <U-BOOT BASE>/arch/arm/dts/k3-j784s4-ddr.dtsi . Please note this change applies to memorycontroller3 only.

https://git.ti.com/cgit/ti-u-boot/ti-u-boot/tree/arch/arm/dts/k3-j784s4-ddr.dtsi?h=08.04.01.005

memorycontroller3: memorycontroller@29f0000 {

compatible = "ti,j721s2-ddrss";

reg = <0x0 0x029f0000 0x0 0x4000>,

<0x0 0x0114000 0x0 0x100>;

reg-names = "cfg", "ctrl_mmr_lp4";

power-domains = <&k3_pds 194 TI_SCI_PD_SHARED>,

<&k3_pds 139 TI_SCI_PD_SHARED>;

clocks = <&k3_clks 194 1>, <&k3_clks 78 2>;

ti,ddr-freq0 = <DDRSS_PLL_FREQUENCY_0>;

ti,ddr-freq1 = <DDRSS_PLL_FREQUENCY_1>;

ti,ddr-freq2 = <DDRSS_PLL_FREQUENCY_2>;

ti,ddr-fhs-cnt = 10; // Changed from <DDRSS_PLL_FHS_CNT> to 10