Other Parts Discussed in Thread: SYSCONFIG,

Dear all,

We've met a confused phenomenon for MCSPI0 transfer data using CCS XDS debug.

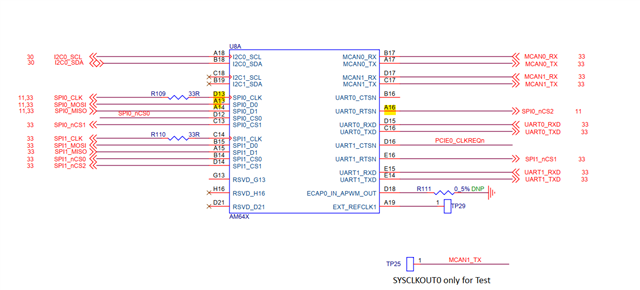

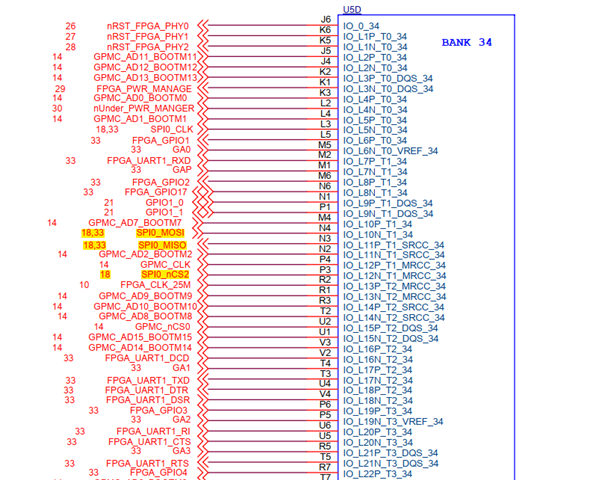

MCSPI0 connect with FPGA use spi 4 wire mode.

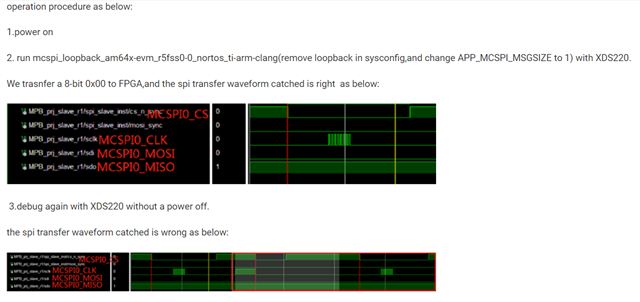

operation procedure as below:

1.power on

2. run mcspi_loopback_am64x-evm_r5fss0-0_nortos_ti-arm-clang(remove loopback in sysconfig,and change APP_MCSPI_MSGSIZE to 1) with XDS220.

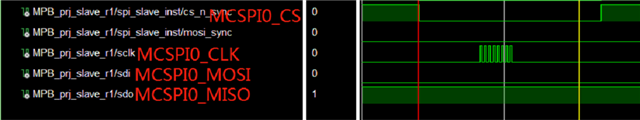

We trasnfer a 8-bit 0x00 to FPGA,and the spi transfer waveform catched is right as below:

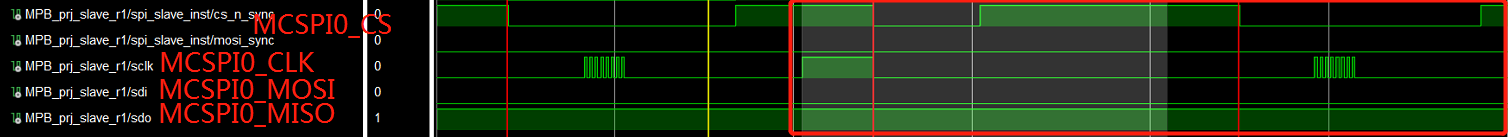

3.debug again with XDS220 without a power off.

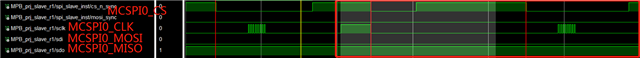

the spi transfer waveform catched is wrong as below:

there are a twice time CS assertion,the first time is invalid, Only the sencod time is valid.

MCSPI0_CLK deassertion should be low-level,but after setp 2 it's sustain a high-level for a while.This phenomenon is right?

Soc:AM6442

MCU PLUS SDK ver:8.2.0.31

CCS ver:11.1.0.00011

syscfg:1.11.0

Thanks,

jimin.li