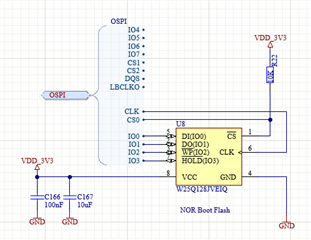

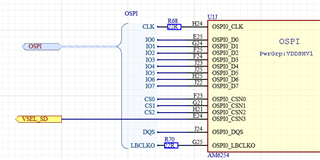

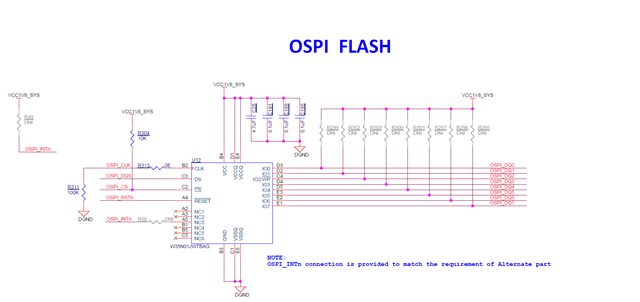

We are facing problem when connecting a SPI Nor (W25Q128VEIQ) to OSPI CS0.

Basically it is working but from time to time it comes to errors during SF PROBE command in u.boot.

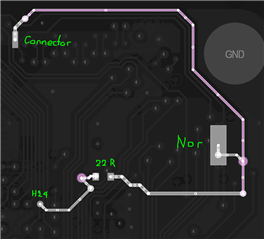

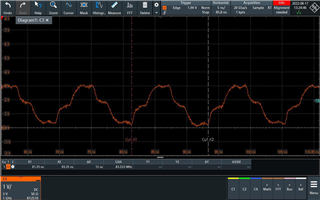

Please find attached the CLK Signal measured during sf probe.

Do you have any advice why the CLK Singal has this strange shape?

The CLK is running at 83.3Mhz

Many thanks and best regards

Stephan