Other Parts Discussed in Thread: TDA4VM

Hi TI team,

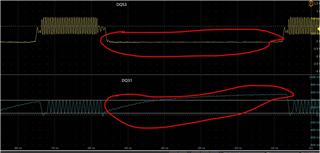

In out custom TDA4VM we are working with New DDR part from micron (MT53E1G32D2FW-046 AUT:B) in which we are seeing following waveform capture.

Normally during idle mode, the DQ should be from high to low. If the DDR controller configuration is incorrect do we see this issue. i have attached the DDR configuration spreadsheet we have used to generate the DDR configurations. Please have a look and let us know if any further changes required.

k3-j721e-ddr-evm-lp4-4266_13_09_22.zip

Regards,

Chaitanya