Part Number: TMDS64GPEVM

Hi experts,

My customer is evaluating PCIe using TMDS64GPEVM and is having problems.

Could you help me with the following questions?

[Detail]

- Evaluation board : TMDS64GPEVM

- Development environment: Code Composer Studio 12.0.0.00009 win64

- Core used: MAIN_Cortex_R5_0_0

- SDK: AM64x MCU+ SDK 08.04.00

- Example: examples/drivers/pcie/pcie_buf_transfer/pcie_buf_transfer_ep

- Refer to: software-dl.ti.com/.../EXAMPLES_DRIVERS_PCIE_BUF_TRANSFER_EP.html

They are checking the following procedure.

- The PCI Express slot is connected to the host PC by a cross cable with PCIE edges on both ends.

- After resetting the CPU with CCS, they load the program from SDK to R5 core and run it in resume.

- When the host PC is turned on, the BIOS screen may freeze. If it does not freeze, the evaluation board is recognized.

Question 1

They are using an evaluation board with a PCI Express End Point and connecting it to a host PC. However, the host PC often freezes.

Do you know what the problem is?

Question 2

After the host PC recognizes the evaluation board, when they reboot the host PC, it always freezes in the state before the BIOS screen.

Does they need to add some reset process to the program?

Question 3

PCI Express must complete initialization within 100ms after power-on.

Is there a way to find out how long it takes for PCI Express initialization to complete on the AM6442 side?

Question 4

How can they change the initial value of configuration space?

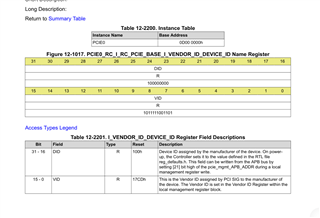

After Pcie_open() in the source code, they was able to change the vendor ID by writing the value directly to the following address

They was able to change the vendor ID.

PCIE0 Physical Address = 0D10 0044h : PCIE0_I_VENDOR_ID_REG Register

Only device ID could be changed with the following address.

PCIE0 Physical Address = 0D00 0000h : PCIE0_I_VENDOR_ID_DEVICE_ID Register

Class code etc. could not be changed with the following address.

PCIE0 Physical Address = 0D00 0008h : PCIE0_I_REVISION_ID_CLASS_CODE Register

However, adding the above code will increase the probability of freezing on the host PC side, so we do not think it is the right way.

Question 5.

When accessing the base address from the host PC, How can they detect read/write on R5 core?

Best regards,

O.H