Hi Ti's Experts,

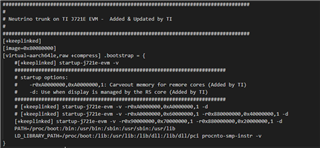

We have some problems about the DDR memory map. The fuse is that the DDR_SHARED_MEM we need has exceeded the preset value. So we want to reduce some memory from other places and add it to DDR_SHARED_MEM.

The SDK used in Board is 7.03. and QNX system.

It found that 0x0_8000_0000 ~ 0x0_9FFF_FFFF was allocated to the QNX system,, so we want ro reduce them to 0x0_8000_0000 ~ 0x0_8FFF_FFFF, Allocate more memory to DDR_SHARED_MEM. This means that the DDR of TI will be allocated from 0x90000000.

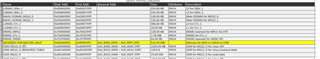

then run ./gen_linker_mem_map.py and The following MAP is obtained,

| Name | Start Addr | End Addr | Size | Attributes | Description |

|---|---|---|---|---|---|

| L2RAM_C66x_1 | 0x00800000 | 0x00837FFF | 224.00 KB | RWIX | L2 for C66x_1 |

| L2RAM_C66x_2 | 0x00800000 | 0x00837FFF | 224.00 KB | RWIX | L2 for C66x_2 |

| MAIN_OCRAM_MCU2_0 | 0x03600000 | 0x0361FFFF | 128.00 KB | RWIX | Main OCRAM for MCU2_0 |

| MAIN_OCRAM_MCU2_1 | 0x03620000 | 0x0363FFFF | 128.00 KB | RWIX | Main OCRAM for MCU2_1 |

| L2RAM_C7x_1 | 0x64800000 | 0x64877FFF | 480.00 KB | RWIX | L2 for C7x_1 |

| L1RAM_C7x_1 | 0x64E00000 | 0x64E03FFF | 16.00 KB | RWIX | L1 for C7x_1 |

| MSMC_MPU1 | 0x70000000 | 0x7001FFFF | 128.00 KB | RWIX | MSMC reserved for MPU1 for ATF |

| MSMC_C7x_1 | 0x70020000 | 0x707E7FFF | 7.78 MB | RWIX | MSMC for C7x_1 |

| MSMC_DMSC | 0x707F0000 | 0x707FFFFF | 64.00 KB | RWIX | MSMC reserved for DMSC IPC |

| DDR_MCU1_0_IPC | 0x90000000 | 0x900FFFFF | 1024.00 KB | RWIX | DDR for MCU1_0 for Linux IPC |

| DDR_MCU1_0_RESOURCE_TABLE | 0x90100000 | 0x901003FF | 1024 B | RWIX | DDR for MCU1_0 for Linux resource table |

| DDR_MCU1_0 | 0x90100400 | 0x90FFFFFF | 15.00 MB | RWIX | DDR for MCU1_0 for code/data |

| DDR_MCU1_1_IPC | 0x91000000 | 0x910FFFFF | 1024.00 KB | RWIX | DDR for MCU1_1 for Linux IPC |

| DDR_MCU1_1_RESOURCE_TABLE | 0x91100000 | 0x911003FF | 1024 B | RWIX | DDR for MCU1_1 for Linux resource table |

| DDR_MCU1_1 | 0x91100400 | 0x91FFFFFF | 15.00 MB | RWIX | DDR for MCU1_1 for code/data |

| DDR_MCU2_0_IPC | 0x92000000 | 0x920FFFFF | 1024.00 KB | RWIX | DDR for MCU2_0 for Linux IPC |

| DDR_MCU2_0_RESOURCE_TABLE | 0x92100000 | 0x921003FF | 1024 B | RWIX | DDR for MCU2_0 for Linux resource table |

| DDR_MCU2_0 | 0x92100400 | 0x93FFFFFF | 31.00 MB | RWIX | DDR for MCU2_0 for code/data |

| DDR_MCU2_1_IPC | 0x94000000 | 0x940FFFFF | 1024.00 KB | RWIX | DDR for MCU2_1 for Linux IPC |

| DDR_MCU2_1_RESOURCE_TABLE | 0x94100000 | 0x941003FF | 1024 B | RWIX | DDR for MCU2_1 for Linux resource table |

| DDR_MCU2_1 | 0x94100400 | 0x95FFFFFF | 31.00 MB | RWIX | DDR for MCU2_1 for code/data |

| DDR_MCU3_0_IPC | 0x96000000 | 0x960FFFFF | 1024.00 KB | RWIX | DDR for MCU3_0 for Linux IPC |

| DDR_MCU3_0_RESOURCE_TABLE | 0x96100000 | 0x961003FF | 1024 B | RWIX | DDR for MCU3_0 for Linux resource table |

| DDR_MCU3_0 | 0x96100400 | 0x96FFFFFF | 15.00 MB | RWIX | DDR for MCU3_0 for code/data |

| DDR_MCU3_1_IPC | 0x97000000 | 0x970FFFFF | 1024.00 KB | RWIX | DDR for MCU3_1 for Linux IPC |

| DDR_MCU3_1_RESOURCE_TABLE | 0x97100000 | 0x971003FF | 1024 B | RWIX | DDR for MCU3_1 for Linux resource table |

| DDR_MCU3_1 | 0x97100400 | 0x97FFFFFF | 15.00 MB | RWIX | DDR for MCU3_1 for code/data |

| DDR_C66x_2_IPC | 0x98000000 | 0x980FFFFF | 1024.00 KB | RWIX | DDR for C66x_2 for Linux IPC |

| DDR_C66x_1_RESOURCE_TABLE | 0x98100000 | 0x981003FF | 1024 B | RWIX | DDR for C66x_1 for Linux resource table |

| DDR_C66x_1_BOOT | 0x98200000 | 0x982003FF | 1024 B | RWIX | DDR for C66x_1 for boot section |

| DDR_C66x_1 | 0x98200400 | 0x98FFFFFF | 14.00 MB | RWIX | DDR for C66x_1 for code/data |

| DDR_C66x_1_IPC | 0x99000000 | 0x990FFFFF | 1024.00 KB | RWIX | DDR for C66x_1 for Linux IPC |

| DDR_C66x_2_RESOURCE_TABLE | 0x99100000 | 0x991003FF | 1024 B | RWIX | DDR for C66x_2 for Linux resource table |

| DDR_C66x_2_BOOT | 0x99200000 | 0x992003FF | 1024 B | RWIX | DDR for C66x_2 for boot section |

| DDR_C66x_2 | 0x99200400 | 0x99FFFFFF | 14.00 MB | RWIX | DDR for C66x_2 for code/data |

| DDR_C7x_1_IPC | 0x9A000000 | 0x9A0FFFFF | 1024.00 KB | RWIX | DDR for C7x_1 for Linux IPC |

| DDR_C7x_1_RESOURCE_TABLE | 0x9A100000 | 0x9A1003FF | 1024 B | RWIX | DDR for C7x_1 for Linux resource table |

| DDR_C7x_1_BOOT | 0x9A200000 | 0x9A2003FF | 1024 B | RWIX | DDR for C7x_1 for boot section |

| DDR_C7x_1_VECS | 0x9A400000 | 0x9A403FFF | 16.00 KB | RWIX | DDR for C7x_1 for vecs section |

| DDR_C7x_1_SECURE_VECS | 0x9A600000 | 0x9A603FFF | 16.00 KB | RWIX | DDR for C7x_1 for secure vecs section |

| DDR_C7x_1 | 0x9A604000 | 0x9EFFFFFF | 73.98 MB | RWIX | DDR for C7x_1 for code/data |

| IPC_VRING_MEM | 0xA0000000 | 0xA1FFFFFF | 32.00 MB | Memory for IPC Vring's. MUST be non-cached or cache-coherent | |

| APP_LOG_MEM | 0xA2000000 | 0xA203FFFF | 256.00 KB | Memory for remote core logging | |

| TIOVX_OBJ_DESC_MEM | 0xA2040000 | 0xA5FDFFFF | 63.62 MB | Memory for TI OpenVX shared memory. MUST be non-cached or cache-coherent | |

| PCIE_QUEUE_SHARED_MEM | 0xA5FE0000 | 0xA5FEFFFF | 64.00 KB | Memory for IPC over PCIe using shared memory. MUST be non-cached or cache-coherent | |

| PCIE_QUEUE_MIRROR_REMOTE_SHARED_MEM | 0xA5FF0000 | 0xA5FFFFFF | 64.00 KB | Reserved Memory for RAT mapping of remote PCIe IPC shared memory. MUST be non-cached or cache-coherent | |

| TIOVX_LOG_RT_MEM | 0xA6000000 | 0xA7FFFFFF | 32.00 MB | Memory for TI OpenVX shared memory for Run-time logging. MUST be non-cached or cache-coherent | |

| DDR_SHARED_MEM | 0xA8000000 | 0xD7FFFFFF | 768.00 MB | Memory for shared memory buffers in DDR | |

| DDR_MCU2_0_NON_CACHE | 0xD8000000 | 0xD8FFFFFF | 16.00 MB | RWIX | DDR for MCU2_0 for non-cached heap |

| DDR_MCU2_1_NON_CACHE | 0xD9000000 | 0xDFFFFFFF | 112.00 MB | RWIX | DDR for MCU2_1 for non-cached heap |

| DDR_MCU1_0_LOCAL_HEAP | 0xE0000000 | 0xE07FFFFF | 8.00 MB | RWIX | DDR for MCU1_0 for local heap |

| DDR_MCU1_1_LOCAL_HEAP | 0xE0800000 | 0xE0FFFFFF | 8.00 MB | RWIX | DDR for MCU1_1 for local heap |

| DDR_MCU2_0_LOCAL_HEAP | 0xE1000000 | 0xE1FFFFFF | 16.00 MB | RWIX | DDR for MCU2_0 for local heap |

| DDR_MCU2_1_LOCAL_HEAP | 0xE2000000 | 0xE2FFFFFF | 16.00 MB | RWIX | DDR for MCU2_1 for local heap |

| DDR_MCU3_0_LOCAL_HEAP | 0xE3000000 | 0xE37FFFFF | 8.00 MB | RWIX | DDR for MCU3_0 for local heap |

| DDR_MCU3_1_LOCAL_HEAP | 0xE3800000 | 0xE3FFFFFF | 8.00 MB | RWIX | DDR for MCU3_1 for local heap |

| DDR_C66X_1_LOCAL_HEAP | 0xE4000000 | 0xE4FFFFFF | 16.00 MB | RWIX | DDR for c66x_1 for local heap |

| DDR_C66X_1_SCRATCH | 0xE5000000 | 0xE7FFFFFF | 48.00 MB | RWIX | DDR for c66x_1 for Scratch Memory |

| DDR_C66X_2_LOCAL_HEAP | 0xE8000000 | 0xE8FFFFFF | 16.00 MB | RWIX | DDR for c66x_2 for local heap |

| DDR_C66X_2_SCRATCH | 0xE9000000 | 0xEBFFFFFF | 48.00 MB | RWIX | DDR for c66x_2 for Scratch Memory |

| DDR_C7X_1_SCRATCH | 0xEC000000 | 0xFBFFFFFF | 256.00 MB | RWIX | DDR for c7x_1 for Scratch Memory |

| DDR_C7X_1_LOCAL_HEAP | 0x100000000 | 0x11FFFFFFF | 512.00 MB | RWIX | DDR for c7x_1 for local heap |

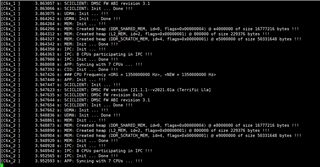

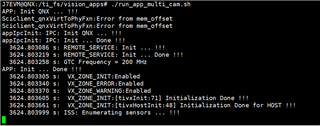

We also modified the r5_mpu.xs of each MCU. After writing to TDA4, the QNX system can be started normally and the memory was changed successfully

But the IPC communication was abnormal. I changed the address back to 0xA0000000 and it was normal. Why this is so? Is there ang places I haven't changed to ? How can I make changes to make IPC communication normal?

Please give me some advice,and Look forward to your reply!