Hi team,

I tried to enable the GPIO1_2 interrupt on the MCU1_0 core using the usb_c_handler.c example, It is found that the interrupt function is not penalized,But it can output high and low levels normally.Print the debug and measured GPIO1_2 port level to find that the level has changed, It indicates that the level is changing, but there is no entry interrupt

Our SDK version is SDK7_1.

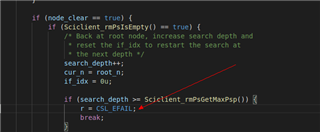

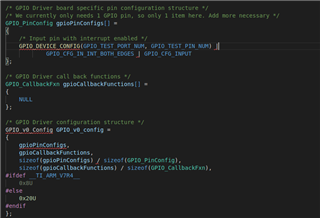

Here's some code:

Why can't enter the interrupt?

Best Regards,

bingxian