Hi,

How to run the direct SPI-BOOT example on TI-C6657-EVM without IBL ?

Regards

Shankari G

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

How to run the direct SPI-BOOT example on TI-C6657-EVM without IBL ?

Regards

Shankari G

How to run the direct SPI-BOOT example on TI-C6657-EVM without IBL ?

===========================================================

Pre-requisite

=====================================

Steps: -- Rebuilding the SPI BOOT EXAMPLE

======================================

Step 1:

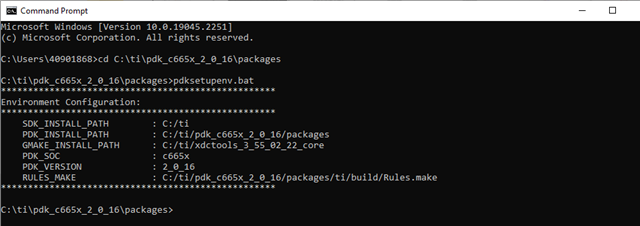

Open command prompt

Go to path "C:\ti\pdk_c665x_2_0_16\packages"

Run the "pdksetupenv.bat"

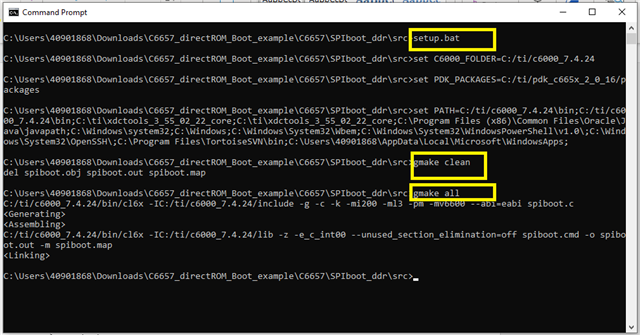

Setup C6000 compiler path in the file "setup.bat" and copy into the src folder and run the "setup.bat" file from windows command line.

set C6000_FOLDER=C:/ti/c6000_7.4.24

set PDK_PACKAGES=C:/ti/pdk_c665x_2_0_16/packages

set PATH=%C6000_FOLDER%\bin;%PATH%

Step2: Change directory to src and build the application binary:

Step3: Copy the spiboot.out to build folder - "C6657_directROM_Boot_example\C6657\SPIboot_ddr\build"

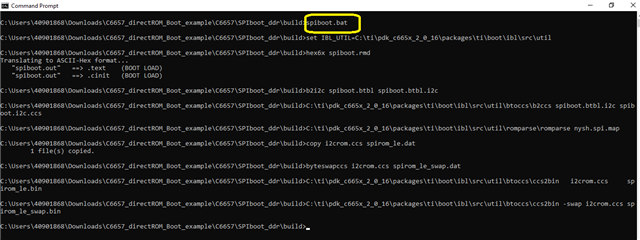

Step4: Set IBL_UTIL path in the spiboot.bat file to the IBL utils folder of PDK of Processor SDK 6.3.

set IBL_UTIL=C:\ti\pdk_c665x_2_0_16\packages\ti\boot\ibl\src\util

hex6x spiboot.rmd

b2i2c spiboot.btbl spiboot.btbl.i2c

%IBL_UTIL%\btoccs\b2ccs spiboot.btbl.i2c spiboot.i2c.ccs

%IBL_UTIL%\romparse\romparse nysh.spi.map

copy i2crom.ccs spirom_le.dat

byteswapccs i2crom.ccs spirom_le_swap.dat

%IBL_UTIL%\btoccs\ccs2bin i2crom.ccs spirom_le.bin

%IBL_UTIL%\btoccs\ccs2bin -swap i2crom.ccs spirom_le_swap.bin

Step 5: Run spiboot.bat file to generate the boot image spirom_le_swap.dat.

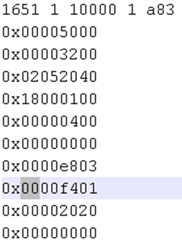

Important Note: Open the spirom_le_swap.dat in CCS and change the value at 0x1F offset as "00" if it has value " 0x51"

Step 6 : Copy the "spirom_le_swap.dat" as "app.dat" into the "C6657_directROM_Boot_example\C6657\SPIboot_ddr\bin\flashwriter"

========

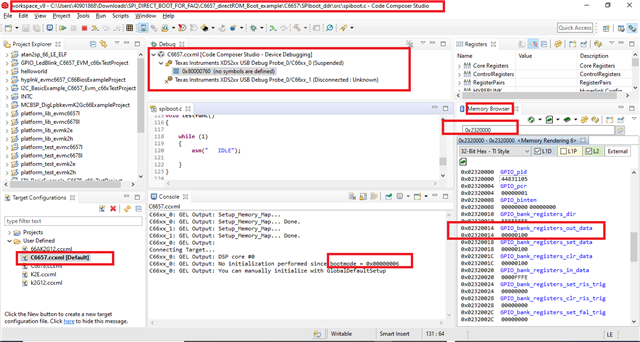

Just to make sure that the SPI-boot on the C6657 core is successful,

I have included a piece of GPIO code. Let us set a value in one of the GPIO registers and try to observe the same value using the CCS memory Window.

/* Copyright (C) 2014 Texas Instruments Incorporated - http://www.ti.com/

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. */

#include <stdio.h>

#include <string.h>

#include <stdint.h>

#include "tiboot.h"

#include "platform.h"

#pragma DATA_SECTION (emif4Cfg, ".emif4Cfg")

const BOOT_EMIF4_TBL_T emif4Cfg = {

BOOT_EMIF4_ENABLE_MSW_pllCtl | \

BOOT_EMIF4_ENABLE_MSW_sdRamTiming1 | \

BOOT_EMIF4_ENABLE_MSW_sdRamTiming2 | \

BOOT_EMIF4_ENABLE_MSW_sdRamTiming3 | \

BOOT_EMIF4_ENABLE_MSW_ddrPhyCtl1 | \

BOOT_EMIF4_ENABLE_MSW_sdRamRefreshCtl | \

BOOT_EMIF4_ENABLE_MSW_sdRamOutImpdedCalCfg | \

BOOT_EMIF4_ENABLE_MSW_sdRamConfig,

BOOT_EMIF_ENABLE_SLSW_config0 | \

BOOT_EMIF_ENABLE_SLSW_config6 | \

BOOT_EMIF_ENABLE_SLSW_config7 | \

BOOT_EMIF_ENABLE_SLSW_config8 | \

BOOT_EMIF_ENABLE_SLSW_config9 | \

BOOT_EMIF_ENABLE_SLSW_config10 | \

BOOT_EMIF_ENABLE_SLSW_config18 | \

BOOT_EMIF_ENABLE_SLSW_config19 | \

BOOT_EMIF_ENABLE_SLSW_config20 | \

BOOT_EMIF_ENABLE_SLSW_config22 | \

BOOT_EMIF_ENABLE_SLSW_config12 | \

BOOT_EMIF_ENABLE_SLSW_config23 | \

BOOT_EMIF_ENABLE_SLSW_config21, /* Config select slsw */

0, /* Config select lsw */

3, /* pllPrediv */

40, /* pllMult */

2, /* pllPostDiv */

0x62477AB2, /* sdRamConfig */

0, /* sdRamConfig2, dont care*/

0x0000144F, /* sdRamRefreshCtl */

0x1333780C, /* sdRamTiming1 */

0x30717FE3, /* sdRamTiming2 */

0x559F86AF, /* sdRamTiming3 */

0, /* lpDdrNvmTiming, dont care */

0, /* powerManageCtl, dont care */

0, /* iODFTTestLogic, dont care */

0, /* performCountCfg, dont care */

0, /* performCountMstRegSel, dont care */

0, /* readIdleCtl, dont care */

0, /* sysVbusmIntEnSet, dont care */

0x70074c1f, /* sdRamOutImpdedCalCfg, dont care */

0, /* tempAlterCfg, dont care */

0x0010010F, /* ddrPhyCtl1 */

0, /* ddrPhyCtl2, dont care */

0, /* priClassSvceMap, dont care */

0, /* mstId2ClsSvce1Map, dont care */

0, /* mstId2ClsSvce2Map, dont care */

0, /* eccCtl, dont care */

0, /* eccRange1, dont care */

0, /* eccRange2, dont care */

0, /* rdWrtExcThresh, dont care */

0x87A0047F, 0, 0, 0, 0, 0, 0x33, 0x3A,

0x2C, 0x2C, 0x21, 0, 0xAF00002, 0, 0, 0,

0, 0, 0xB7, 0xB1, 0xA4, 0xA4, 0x98, 0x200,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0, 0, 0, 0, 0, 0

};

#define GPIO_BASE (0x2320000)

#define GPIO_DIR_OFFSET (0x10)

#define GPIO_SETDATA_OFFSET (0x18)

#define GPIO_CLEARDATA_OFFSET (0x1C)

void testfunc();

void testfunc()

{

while (1)

{

asm(" IDLE");

}

}

void main(void)

{

volatile uint32_t *reg_val;

reg_val = (volatile uint32_t *)(GPIO_BASE + GPIO_DIR_OFFSET);

// configure as output pin -- write 0 to the Direction register

*reg_val &= ~ (1 << 8);

reg_val = (volatile uint32_t *) (GPIO_BASE + GPIO_SETDATA_OFFSET);

// Write value 1 in the set data register, so that Out data register will be 1

*reg_val |= (1 << 8);

testfunc();

}

Replace the above code in spiboot.c

Repeat all the steps from 1 - 6

====

============================================================================

Steps: -- Flashing the SPI-BOOT code into the NOR flash memory using the NOR-Writer utility.

============================================================================

Now, after the step6, you will have the app.dat in ---- "C6657_directROM_Boot_example\C6657\SPIboot_ddr\bin\flashwriter" where the norwriter.out is present.

======

1. Boot EVM in No Boot mode.

SW3 {pin 0 - pin8) = 10000000 (0-ON, 1-OFF)

SW5(pin0 - pin8) = 00000000

2. Launch CCS and connect to C6657-core 0. Let the GEL file run to initialize PLL and DDR memory.

3. Go to the bin/flashwriter and ensure that norwriter_input_txt points to "app.dat"

4. In CCS load memory location 0x80000000 using memory browser. Load norwriter.out file and run.

For full instructions for flashing the boot image to SPI NOR refer to README (C6657) in the NORwriter package in Processor SDK.

=================================

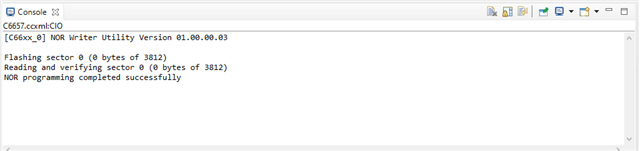

Output console messages when executing NOR-Writer.out

The same flashing steps are given in the video below.

==========

5. Reboot EVM into direct SPI mode. To do this, configure dip switches:

SW3 {pin 0 - pin8) = 10110000 (0-ON, 1-OFF)

SW5(pin0 - pin8) = 00100000

6. On power up connect to Core0 using CCS, the DDR should be configured by the boot image.

To test, connect to GEM core 0 and navigate to address 0x80000000 in the memory browser in CCS

and

It will display the bootmode value as "6" in the console -- SPI boot mode as per the data sheet

7. Go to memory browser window and feed the GPIO register address as "0x2320000 " .

Please note that the value is "00000100" in GPIO_bank_registers_out_data.

============

Regards

Shankari G