Hi,

My customer has developed their PCB board with AM5706, but it can’t start up.

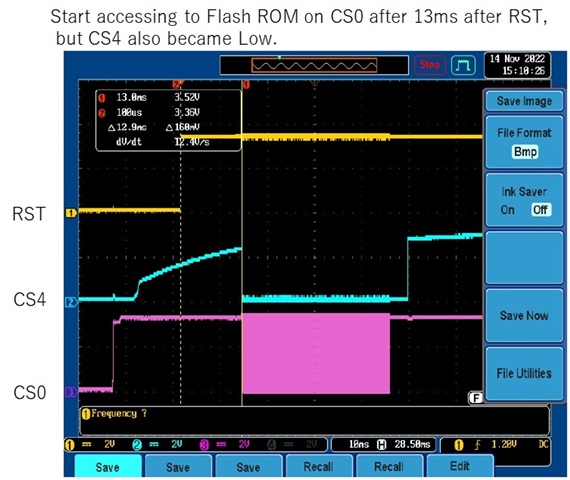

They’re setting the Sysboot as XIP memory booting from Flash ROM on CS0, but the Flash cannot be read, because CS4 which SRAM is connected to also became Low as Active at the same time. See the attached waveform.

Do you know why the both CS0 and CS4 became Low after Reset ? Could you give them any advice ?

Sysboot = 0b 1 00 0 01 00 10 0101

Memory Preferred Booting

0b10 0b0101 1st XIP 2nd SD 3rd USB

0b01 SYS_CLK1 Speed : 20MHz

0b0 Disable Wait-pin Monitoring for Read Access

0b00 Non-Muxed device

0b1 16-bit Bus width

Regards,

Hideaki