Hi, TI

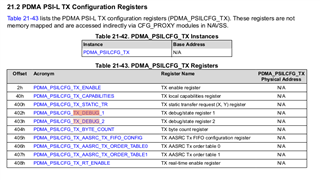

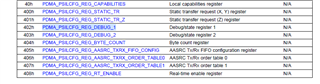

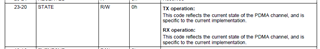

I have a question about Safety Mechanism PDMA7 "Software Monitoring of Hardware State". In the safety manual, it requires to monitor the debug register(PDMA_PSILCFG_REG_DEBUG_1

PDMA_PSILCFG_REG_DEBUG_2), but how can I judge that PDMA state is incorrect through these debug registers?

Could you give me an example?

Thank you!

Zhihua