TDA4VM PSDK 8.4.0.6 J721E is normal with a app displaying images.

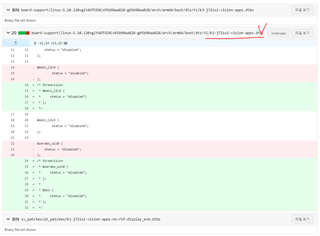

But TIDSS SYNC LOST happens in TDA4AL PSDK 8.4.0.6 J721S2.

The error message & result video same as below.

Error message in UART

[ 169.525066] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 172.977865] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 173.443758] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 174.477367] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 175.243961] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 175.277356] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 175.577444] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 175.643513] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 177.978272] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 178.143707] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 178.149196] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 178.378223] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 184.911079] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 185.843364] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 186.676760] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 188.844462] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 189.344132] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 189.644108] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 189.909652] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 190.844142] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 190.876443] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 190.943731] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 191.011178] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 191.177044] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 191.610774] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 193.376862] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 193.409827] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 193.443302] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 193.576447] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 197.543594] tidss_crtc_error_irq: 4 callbacks suppressed [ 197.543608] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 197.575880] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 197.809839] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 198.243392] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 198.601502] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 198.843209] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 200.376214] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 200.408766] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 200.909571] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 200.943035] tidss 4a00000.dss: CRTC0 SYNC LOST: (irq 80) [ 207.409597] tidss_crtc_error_irq: 4 callbacks suppressed

Result video - display is often broken

- full video link -

http://119.202.38.9:5000/sharing/hBj84MDzV

Could I get some help ?