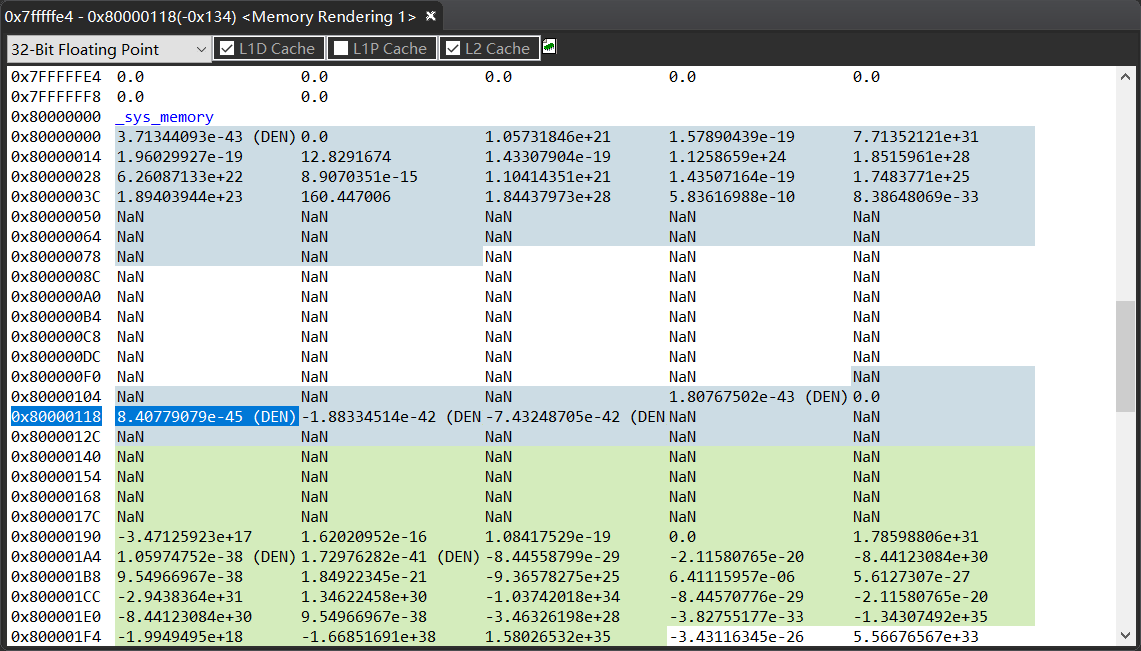

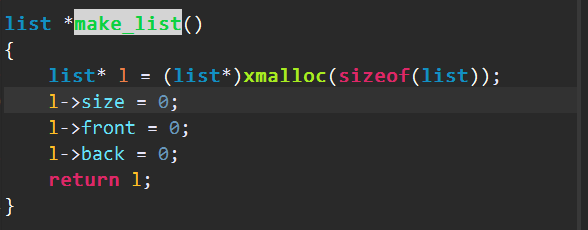

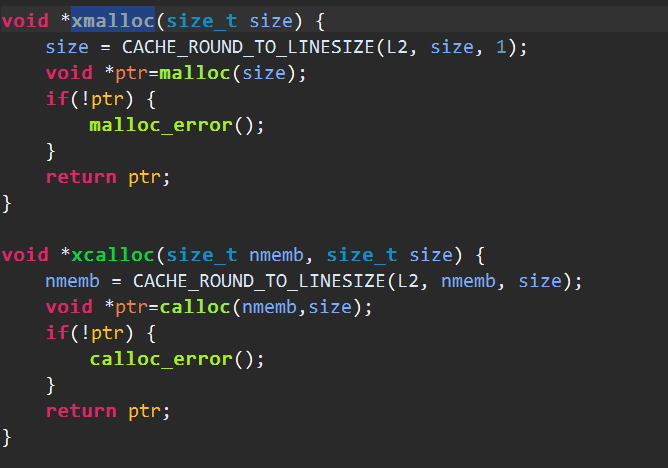

In .cmd, the system field is divided in the DDR space, and then the space is divided by core 0 through malloc and calloc, the divided memory length has been aligned with the L2 cache line length, but its boundary is not aligned to the cache line boundary, as shown in the figure below, list l starts with 0x80000118, and cache line starts with 0x80000110, how to make the divided memory and cache line boundary alignment.