Other Parts Discussed in Thread: TPS6594-Q1, , DRA829

Hi

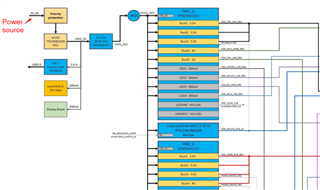

We follow the PDN-0C (two TPS6594-Q1 devices) to power supply the DRA829J processor. The MCU and Main voltage domains are Isolated.

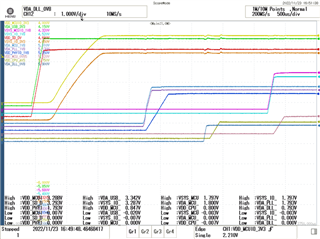

In our design, the power-up sequencing is correct, as shown below figure.

And it matches <Isolated MCU and Main Domains Power- Up Sequencing>, described in the section 7.10.2.4 of DRA829's datasheet.

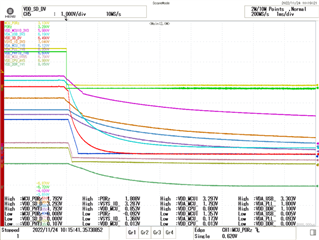

However, there are some doubts in our power-down sequencing.

Shown below figure.

In our desing, we are shutting down the system by directly disconnecting the power source. But the power-down sequencing does not match <Isolated MCU and Main Domains Power- down Sequencing>, described in the section 7.10.2.5 of DRA829's datasheet.

Is this power-down sequencing allowed?

Whether this mismatched power-down sequencing may cause some unpredictable problems?

How should we modify our design?

Best Regards,

Tank