Hi team,

Customers need two embedded chip and the requirements are as follows:

1) digital radio application, modulation demodulation algorithm core DSP chip:

a. Single-core 32-bit fixed-point DSP;

b. Operating frequencies greater than 100m;

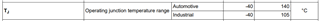

c. Operating temperature -40~85;

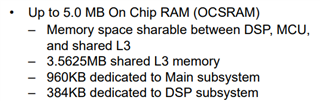

d. 256KB SRAM+64KB DRAM integrated internally, 12KB ROM or higher

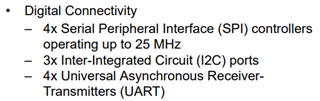

e. 3 I2S, 2 SPI, 1 UART, 1 USB or more

f. Core voltage 1-1.3C

2) master chip Arm processor:

a. 16 bit with a main frequency greater than 150 MHz (greater than or equal to 1 core)

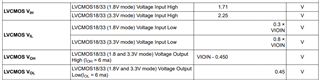

b. Core voltage ≤ 3.3 V, IO voltage ≤ 3.3 V.

c. Instruction cache ≥ 128 KB, data cache ≥ 128 KB

d. number of IO ≥ 80

e. number of PWM outputs ≥ 32

Could you help give some recommendations? Thanks.

Best Regards,

Cherry